### VARIADOR DE FRECUENCIA TRIFÁSICO VSI DE DOS NIVELES CON ESTRATEGIA DE CONTROL PARA MINIMIZAR EL CONTENIDO ARMÓNICO

### AUTOR: HÉCTOR MANUEL ZABALETA MEZA

UNIVERSIDAD DE PAMPLONA

FACULTAD DE INGENIERÍAS Y ARQUITECTURA

DEPARTAMENTO DE INGENIERÍAS ELECTRÓNICA, ELÉCTRICA, SISTEMAS

Y TELECOMUNICACIONES

PROGRAMA DE INGENIERÍA ELÉCTRICA

PAMPLONA, NORTE DE SANTANDER

2017

### VARIADOR DE FRECUENCIA TRIFÁSICO VSI DE DOS NIVELES CON ESTRATEGIA DE CONTROL PARA MINIMIAR EL CONTENIDO ARMÓNICO

### AUTOR: HÉCTOR MANUEL ZABALETA MEZA

Tesis o trabajo de investigación presentada(o) como requisito parcial para optar al título de: **Ingeniero Eléctrico**

Director:

LUIS DAVID PABÓN FERNÁNDEZ

M.Sc. Control Industrial

Codirector:

**EDISON ANDRÉS CAICEDO PEÑARANDA**

Ingeniero Eléctrico

UNIVERSIDAD DE PAMPLONA

FACULTAD DE INGENIERÍAS Y ARQUITECTURA

DEPARTAMENTO DE INGENIERÍAS ELECTRÓNICA, ELÉCTRICA, SISTEMAS

Y TELECOMUNICACIONES

PROGRAMA DE INGENIERÍA ELÉCTRICA

PAMPLONA, NORTE DE SANTANDER

2017

# VARIADOR DE FRECUENCIA TRIFÁSICO VSI DE DOS NIVELES CON ESTRATEGIA DE CONTROL PARA MINIMIZAR EL CONTENIDO ARMÓNICO

FECHA DE INICIO DEL TRABAJO: ABRIL DE 2017. FECHA DE TERMINACIÓN DEL TRABAJO: DICIEMBRE DE 2017.

| OMBRES Y FIRMAS DEL DIRECTOR Y JURADOS DE SUSTENTACIÓN: |  |  |  |  |  |  |

|---------------------------------------------------------|--|--|--|--|--|--|

| DIRECTOR: MSC. LUIS DAVID PABÓN FERNÁNDEZ               |  |  |  |  |  |  |

| JURADO 1: PH.D. ALDO PARDO GARCÍA                       |  |  |  |  |  |  |

| JURADO 2: MSC. JORGE LUIS DÍAS RODRIGUEZ                |  |  |  |  |  |  |

UNIVERSIDAD DE PAMPLONA

FACULTAD DE INGENIERÍAS Y ARQUITECTURA

DEPARTAMENTO DE INGENIERÍAS ELECTRÓNICA, ELÉCTRICA, SISTEMAS

Y TELECOMUNICACIONES

PROGRAMA DE INGENIERÍA ELÉCTRICA

PAMPLONA, NORTE DE SANTANDER

2017

(Dedicatoria o lema)

Principalmente, a mi madre por su apoyo y comprensión, sus oraciones y bendiciones para ayudarme a continuar.

A mi padre por contagiarme de su lucha y perseverancia ante cualquier situación.

A todas aquellas personas que están cerca de mí brindando su apoyo y sienten este logro como suyo.

### **Agradecimientos**

A los ingenieros Luis David Pabón Fernández y Edison Andrés Caicedo Peñaranda por la confianza y apoyo. Al Dr. Aldo Pardo García y al decano de la facultad de Ingenierías y Arquitectura de la Universidad de Pamplona Jorge Luis Díaz, sus obras han incentivado el desarrollo de este trabajo.

A mis compañeros de estudio que brindaron su compañía y consejos.

A la Universidad de Pamplona y el programa de Ingeniería Eléctrica por su colaboración académica y administrativa.

#### **Pensamientos**

"No pretendamos que las cosas cambien, si siempre hacemos lo mismo. La crisis es la mejor bendición que puede sucederle a personas y países, porque la crisis trae progresos. La creatividad nace de la angustia como el día nace de la noche oscura. Es en la crisis que nace la inventiva, los descubrimientos y las grandes estrategias. Quien supera la crisis se supera a sí mismo sin quedar 'superado'.

Quien atribuye a la crisis sus fracasos y penurias, violenta su propio talento y respeta más a los problemas que a las soluciones. La verdadera crisis, es la de la incompetencia. El inconveniente de las personas y los países es la pereza para encontrar las salidas y soluciones. Sin crisis no hay desafíos, sin desafíos la vida es una rutina, una lenta agonía. Sin crisis no hay méritos. Es en la crisis donde aflora lo mejor de cada uno, porque sin crisis todo viento es caricia. Hablar de crisis es promoverla, y callar en la crisis es exaltar el conformismo. En vez de esto, trabajemos duro. Acabemos de una vez con la única crisis amenazadora, que es la tragedia de no querer luchar por superarla."

#### **Albert Einstein**

#### Resumen

En este proyecto se diseña un variador de frecuencia trifásico VSI de dos niveles para la implementación en los laboratorios del programa de Ingeniería Eléctrica de la Universidad de Pamplona.

La metodología aplicada consiste en una minuciosa búsqueda bibliográfica de las diferentes topologías de variadores de frecuencia, por consiguiente, la teoría sobre los componentes de electrónica de potencia a utilizar para el diseño, se continúa con las respectivas simulaciones del control aplicado a los componentes semiconductores del inversor trifásico para luego proceder con su construcción. El diseño se realizará teniendo en cuenta los componentes que se encuentran en el mercado y que son más asequibles.

Posteriormente, se realizará el diseño del algoritmo y se aplica al variador de frecuencia para finalmente realizar pruebas y mediciones. Los resultados de estas pruebas y mediciones se compensarán dentro del libro con sus respectivas conclusiones.

**Palabras clave:** armónicos, algoritmo, motor de inducción, PWM, rectificador, inversor, IGBT, opto-acoplador.

#### **Abstract**

In this project, a three-phase VSI two-level frequency inverter is designed for the implementation in the laboratories of the Electrical Engineering program of the University of Pamplona because there is not one that presents good energy quality, high efficiency and low harmonic content.

The applied methodology consists in a meticulous bibliographic search of the different topologies of frequency inverter, therefore, the theory on the components of power electronics to be used for the design, continues with the respective simulations of the control applied to the semiconductor components of the three-phase inverter to then proceed with its construction. The design will be made taking into account the components that are in the market and that are more affordable.

Subsequently, the algorithm design will be performed and applied to the frequency inverter to finally perform tests and measurements. The results of these tests and measurements will be compensated within the book with their respective conclusions.

**Keywords:** harmonics, algorithm, induction motor, PWM, rectifier, inverter, IGBT, opto-coupler

### Contenido

| Р                                                                   | ág.  |

|---------------------------------------------------------------------|------|

| Resumen y Abstract                                                  | . XI |

| Introducción                                                        | .15  |

| 1. INTRODUCCIÓN                                                     | 15   |

|                                                                     |      |

| 2. 3. PLANTEAMIENTO DEL PROBLEMA Y JUSTIFICACIÓN                    |      |

| 2.1 FORMULACIÓN DEL PROBLEMA:2.2 JUSTIFICACIÓN DE LA INVESTIGACIÓN: | . 16 |

| 2.2 JUSTIFICACIÓN DE LA INVESTIGACIÓN:                              | 16   |

| 3. DELIMITACIÓN                                                     | .18  |

| 3.1 OBJETIVO GENERAL:                                               | 18   |

| 3.2 OBJETIVOS ESPECÍFICOS:                                          | 18   |

| 4. CAPÍTULO 1: MARCO TEÓRICO                                        | .19  |

| 4.1 RECTIFICADORES DE DIODOS DE LÍNEA DE FRECUENCIA DE CA – CC .    |      |

| 4.2 RECTIFICADORES TRIFÁSICOS DE PUENTE COMPLETO                    | _    |

| 4.3 TRANSISTORES BIPOLARES DE PUERTA AISLADA (IGBT)                 | 22   |

| 4.4 INVERSORES DE CC – CA DE MODO CONMUTADO                         |      |

| 4.4.1 INVERSORES MODULADOS POR ANCHO DE PULSOS                      | .26  |

| 4.5 INVERSORES TRIFÁSICOS                                           | . 27 |

| 4.5.1 PWM EN INVERSORES TRIFÁSICOS DE FUENTES DE VOLTAJE            |      |

| 4.5.2 CONDUCCIÓN DEL INVERSOR TRIFÁSICO                             |      |

| 4.6 CONVERTIDORES DE FRECUENCIA VARIABLE                            |      |

| 4.6.1 ACCIONAMIENTOS PWM-VSI DE FRECUENCIA VARIABLE                 |      |

| 4.6.2 IMPACTO DE LOS ARMÓNICOS DE PWM-VSI                           |      |

| 4.7 FUNDAMENTOS DE LA MODULACIÓN PWM                                |      |

| 4.7.1 MODULACIÓN PWM BASADA EN PORTADORA (CB-PWM)                   |      |

| 4.8 MÉTODOS PWM CONTINUOS (CPWM)                                    | 35   |

| 4.8.1 LA MODULACIÓN PWM SINUSOIDAL (SPWM)                           | .35  |

| 4.8.2 INYECCIÓN DEL TERCER ARMÓNICO                                 |      |

| 4.8.3 PWM CON VECTORES ESPACIALES BASADA EN PORTADORA               |      |

| 4.9 MÉTODOS PWM DISCONTINUOS [DPWM]                                 |      |

| 4.9.1 DPWM1                                                         |      |

| 4.9.2 DPWMMax                                                       |      |

| 4.9.3 DPWM24.9.4 DPWM0                                              | _    |

| 4.9.4 DPWW0                                                         |      |

|        | 4.9.6 DPWMMin                                           | 45       |

|--------|---------------------------------------------------------|----------|

|        | 4.10 MÉTODOS DPWM HÍBRIDOS                              | 46       |

|        | 4.10.1 MÉTODO PWM DISCONTINUO GENERALIZADO (GENERALIZED | 40       |

|        | DISCONTINUOUS PWM [GDPWM])                              | 46       |

|        | 4.10.2 MÉTODO PWM HÍBRIDO DISCONTINUO                   |          |

|        | 4.10.3 MODULACIÓN PWM DE VECTORES ESPACIALES (SVPWM)    | 47       |

|        | 4.12 CARACTERÍSTICAS DE LAS TÉCNICAS DE MODULACIÓN PWM  | 50<br>52 |

|        | 4.12 CARACTERISTICAS DE LAS TECNICAS DE MODULACIÓN PWM  | 52       |

| 5.     | . CAPÍTULO 2: SIMULACIÓN                                | 54       |

|        | 5.1 SPWM                                                | 54       |

|        | 5.2 SVPWM                                               | 60       |

|        | 5.3 THIPWM                                              | 64       |

| e<br>E | CAPÍTULO 3: DISEÑO                                      | 70       |

| υ.     | 6.1 DIAGRAMA DE BLOQUES DEL INVERSOR                    |          |

|        | 6.2 MÓDULO RECTIFICADOR DE SEIS INTERRUPTORES           |          |

|        | 6.3 FILTRO CAPACITIVO PARA EL RECTIFICADOR              |          |

|        | 6.3.1 CIRCUITO DE CARGA Y DESCARGA DEL CAPACITOR        |          |

|        | 6.4 MODULO PUENTE INVERSOR CON IGBT's                   |          |

|        | 6.4.1 SELECCIÓN DE LOS IGBT's                           |          |

|        | 6.4.2 MÓDULO DE IGBT "SIX-PACK"                         |          |

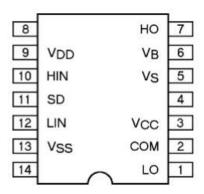

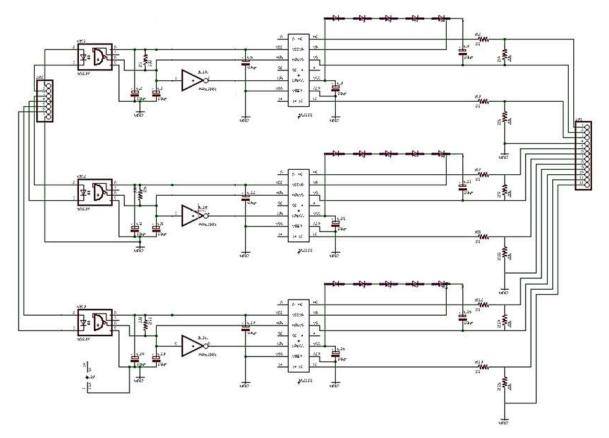

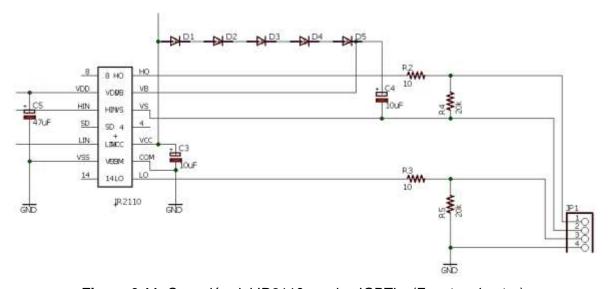

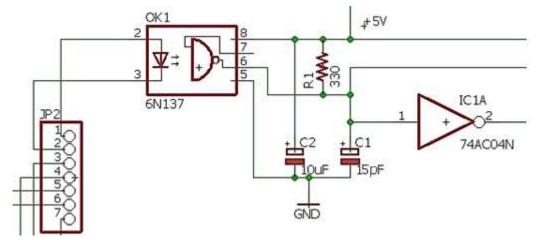

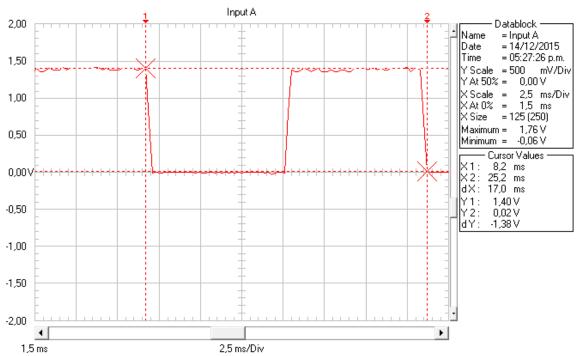

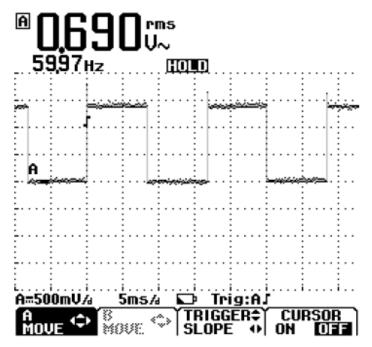

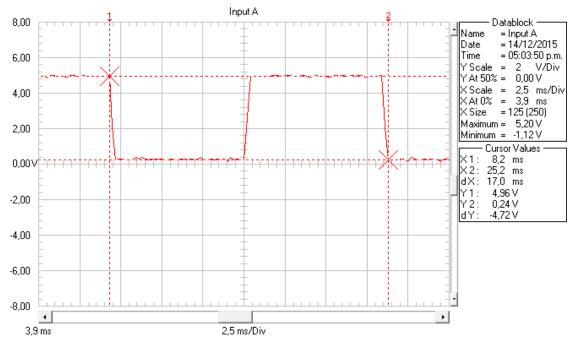

|        | 6.5 CIRCUITO CONTROLADOR DE IGBT's (DRIVER)             | 82       |

|        | 6.5.1 CÁLCULO DE LOS CONDENSADORES                      | 85       |

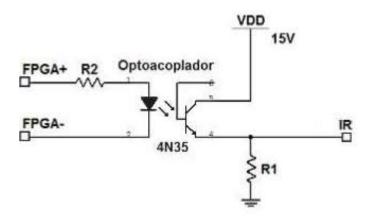

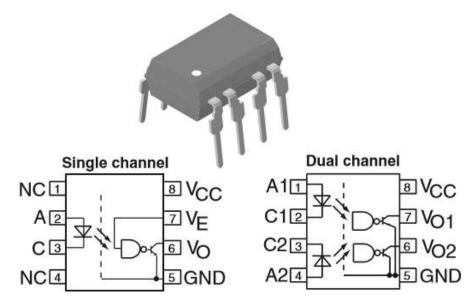

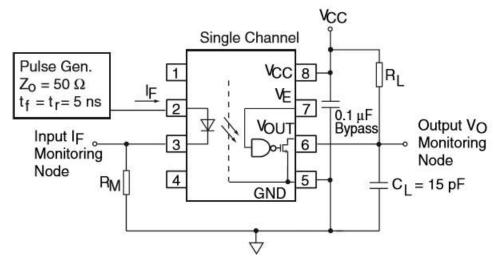

|        | 6.6 CIRCUITOS DE ACOPLAMIENTO ÓPTICO DE SEÑALES         |          |

|        | 6.7 SEÑALES DE CONTROL                                  |          |

|        | 6.8 DISIPADOR DE CALOR                                  |          |

|        | 6.8.1 CÁLCULO DE LA RESISTENCIA TÉRMICA DE UN DISIPADOR |          |

|        | 6.9 CIRCUITO DE ALIMENTACIÓN                            |          |

|        | 6.10 CÁLCULOS DE DISIPADOR DE LOS REGULADORES           |          |

|        | 6.10.1 REGULADOR LM7415                                 |          |

|        | 6.10.2 REGULADOR LM7405                                 |          |

|        | 6.11 PROTECCIONES                                       | 107      |

|        | 6.12 JUSTIFICACIÓN DEL USO DE UNA FPGA                  |          |

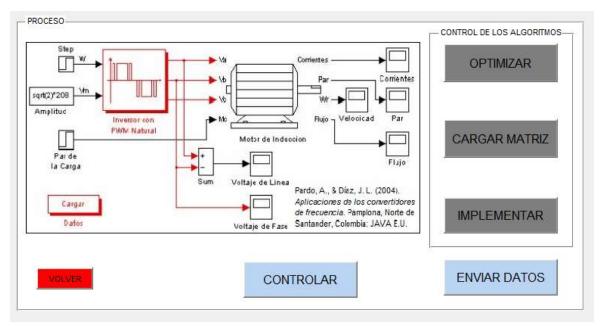

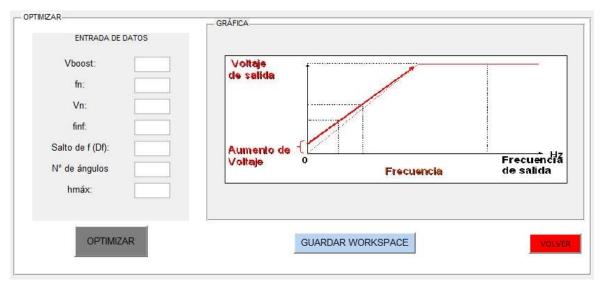

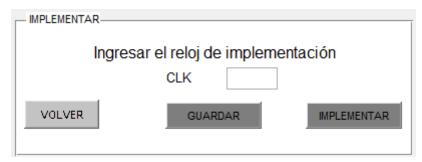

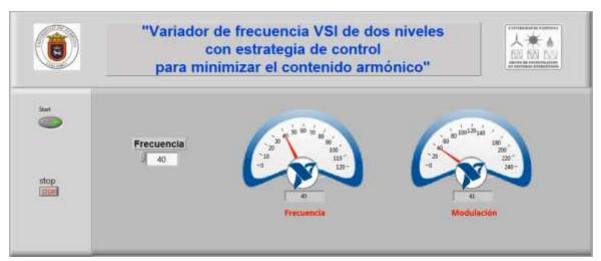

|        | 6.13 INTERFAZ                                           | 108      |

| 7.     | CAPÍTULO 4: ALGORITMO DE OPTIMIZACIÓN                   | 114      |

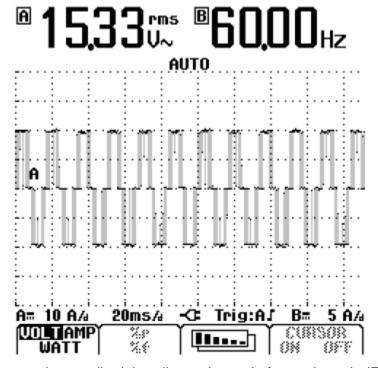

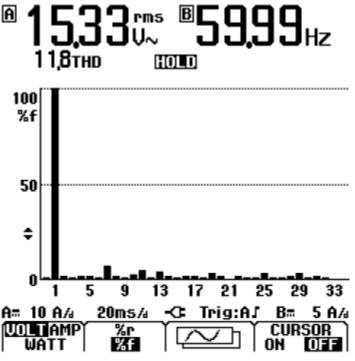

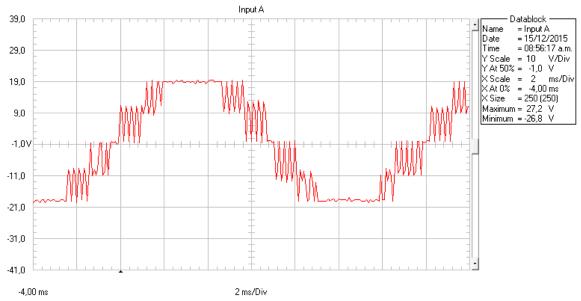

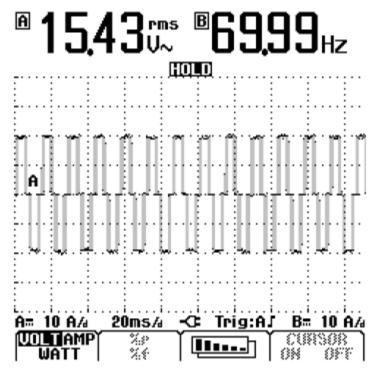

| R      | CAPÍTULO 5: PRUEBAS Y MEDICIONES                        | 123      |

|        |                                                         |          |

| 9.     | CONCLUSIONES Y RECOMENDACIONES                          |          |

|        | 9.1 CONCLUSIONES                                        |          |

|        | 9.2 RECOMENDACIONES                                     | 132      |

| 11     | N RIRI IOGRAFÍA                                         | 136      |

### 1. INTRODUCCIÓN

El presente trabajo consiste en el diseño y construcción de un inversor trifásico utilizando la técnica PWM y algoritmo genético para conseguir una notable reducción del contenido armónico, con elementos de potencia como son los módulos de IGBT's de la FUJI ELECTRIC. Se construirá un módulo funcional cuya aplicación fundamental será en la variación de la velocidad de motores trifásicos de inducción.

Para alcanzar estos objetivos principalmente se presentan sus respectivas aplicaciones y utilidades de los mismos, paso seguido se analiza los circuitos que describen al motor de inducción y su comportamiento al variar sus parámetros lo cual permite determinar y comprender las diferentes formas para controlar al motor con énfasis en el control por voltaje y frecuencia variable con las configuraciones más comunes de inversores. A continuación, se analiza los semiconductores seleccionados IGBT's, para luego describir la modulación sinusoidal de ancho de pulso, la cual permite obtener voltaje y frecuencia variable que es el método más efectivo para el control de motores y usado en el presente trabajo.

Para este trabajo se realiza un algoritmo que permita generar las señales necesarias para sintetizar una onda sinusoidal de amplitud y frecuencia desead. Para el control y monitoreo del sistema se permite la interfaz con el usuario. El siguiente paso es el diseño de la etapa de potencia, la protección y las fuentes de alimentación, de acuerdo a las necesidades para el inversor.

# 2.3. PLANTEAMIENTO DEL PROBLEMA Y JUSTIFICACIÓN

### 2.1 FORMULACIÓN DEL PROBLEMA:

En los cursos de Ingeniería Eléctrica de la Universidad de Pamplona no se cuenta con un variador de frecuencia con bajo contenido armónico para realizar los laboratorios que complementan la parte teórica, estas condiciones dificultan el aprendizaje de los estudiantes.

Los variadores de frecuencia (*Variable Frecuency Drives* - VFD's o *Adjustable Speed Drive* - ASD) han sido utilizados para aplicaciones como el control de procesos y el ahorro de energía sobre las máquinas en la industria moderna que basan su funcionamiento en velocidades variables. Por lo tanto, se debe garantizar un buen servicio por parte de los variadores con el fin obtener los beneficios que estos pueden aportar en cualquier aplicación.

Por otra parte, es bien conocido que los variadores de frecuencia aportan alto grado de contenido armónico en las redes de distribución eléctrica afectando directamente a las máquinas en la industria y degradando su vida útil con armónicos de bajo rango como 5 y 7. En este sentido, después del análisis y observaciones se plantea la problemática y se decide diseñar uno que posteriormente se implemente en los laboratorios del programa de manera didáctica.

### 2.2 JUSTIFICACIÓN DE LA INVESTIGACIÓN:

Los variadores de frecuencia convencionales como se mencionó antes inyectan a la red alto contenido armónico que afecta a las máquinas eléctricas a pesar de ser la mejor opción cuando se requieren velocidades variables en una línea de producción. Como consecuencia, el presente estudio aborda la construcción de un variador de frecuencia trifásico VSI de dos niveles, reduciendo los efectos armónicos del suministro de alimentación. En este sentido es necesario duplicar el número de veces que se obtiene corriente del suministro y, por lo tanto, también reducir la corriente obtenida por cada pulso.

De esta manera, se "nivela" la corriente extraída y el contenido armónico de la línea de suministro. (Guevara, 2013).

En términos generales, este método de gestión de calidad de la alimentación eléctrica se conoce como control de 12 o 6 interruptores. Al igual que el variador de frecuencia "convencional" aporta el control de velocidad sobre el motor y su respectivo ahorro energético. (Rashid, 2004) y (Mohan, Undeland, & Robbins, 2009).

### 3. DELIMITACIÓN

#### 3.1 OBJETIVO GENERAL:

Diseñar e implementar un variador de frecuencia trifásico VSI de dos niveles con estrategia de control para minimizar el contenido armónico y ser utilizado de manera didáctica en los laboratorios del programa.

### 3.2 OBJETIVOS ESPECÍFICOS:

- Diseñar las etapas de potencia correspondiente al variador de frecuencia trifásico VSI de dos niveles.

- Diseñar el algoritmo de control para el variador de frecuencia trifásico.

- Construir el variador de frecuencia trifásico VSI con los respectivos componentes de electrónica de potencia necesaria para su funcionamiento.

- Implementar el algoritmo para minimizar el contenido armónico en el variador de frecuencia trifásico VSI.

- Efectuar pruebas y mediciones del variador de frecuencia trifásico.

### 4. CAPÍTULO 1: MARCO TEÓRICO

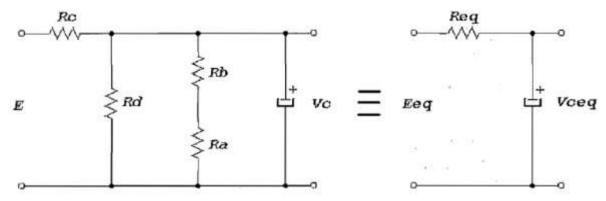

# 4.1 RECTIFICADORES DE DIODOS DE LÍNEA DE FRECUENCIA DE CA – CC NO CONTROLADA

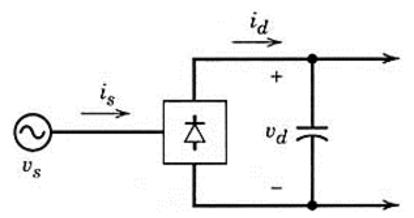

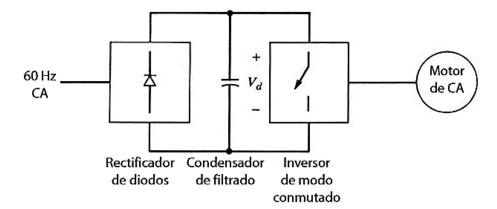

En la mayoría de las aplicaciones de la electrónica de potencia, la entrada de energía se realiza en forma de onda pura de voltaje CA de 50 o 60 Hz que proviene de la fuente principal de alimentación de electricidad y que primero se convierte en un voltaje de CC. Cada vez más, la tendencia es usar los rectificadores económicos con diodos para convertir la CA de entrada en CC en una forma no controlada, mediante rectificadores de diodos como se muestra en la figura 4.1. En estos rectificadores de diodos, el flujo de energía se puede provenir desde el lado CA de la fuente principal de electricidad hacia el lado de CC. La mayoría de las aplicaciones de electrónica de potencia, como los suministros de energía de conmutación de CC, los controles de motores de CA, los servocontroles de CC, etc., utiliza estos rectificadores no controlados. (Mohan, Undeland, & Robbins, 2009).

**Figura 4.1.** Diagrama de un puente de rectificador por diodos. (Mohan, Undeland, & Robbins, 2009).

El voltaje de CC de salida de un rectificador debe estar tan libre de ondulaciones o rizos como sea posible. Por tanto, se conecta un condensador grande como filtro del lado de CC. Este condensador se carga hasta un valor cerca del pico de voltaje de CA de entrada. En consecuencia, la corriente a través del rectificador es muy grande y está cerca del pico del voltaje de CA de entrada. No fluye en forma continua; es decir, se vuelve cero

por periodos finitos durante cada semiciclo de la frecuencia de línea. Estos rectificadores consumen corriente muy distorsionada de la fuente de alimentación principal. Hoy en día, e incluso más en el futuro las normas y lineamientos sobre armónicos limitarán la cantidad de distorsión de corriente que se permite entrar en la electricidad suministrada por las compañías generadoras, y quizá no se permitan los rectificadores de diodo sencillo. (Mohan, Undeland, & Robbins, 2009).

En aplicaciones industriales, la gama de tensiones que cubren estos convertidores va de algunos V hasta varios centenares de kV, en el caso de transporte de energía en corriente continua. La gama de corrientes va de algunos mA hasta algún centenar de kA, en el caso de las instalaciones electroquímicas. (Ballester & Piqué, 2013).

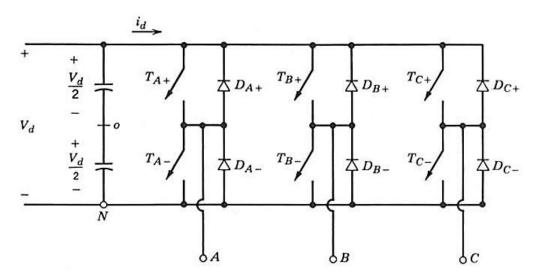

# 4.2 RECTIFICADORES TRIFÁSICOS DE PUENTE COMPLETO

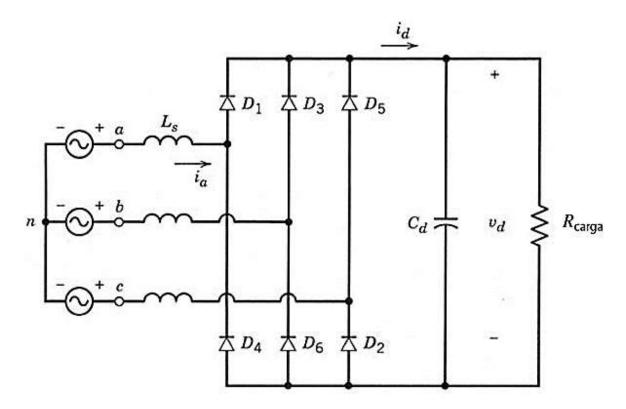

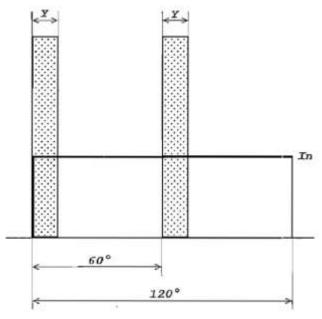

En aplicaciones industriales donde hay disponibilidad de voltajes de CA trifásicos, es preferible usar circuitos de rectificadores trifásicos en lugar de rectificadores monofásicos, por su menor contenido de ondulaciones en las formas de onda y una mayor capacidad de manejo de potencia. El rectificador trifásico de puente completo y seis impulsos que se muestra en la figura 4.2 es un arreglo de circuito de uso común. Un condensador de filtrado está conectado al lado de CC del rectificador. (Mohan, Undeland, & Robbins, 2009).

Este tipo de rectificadores también llamados de onda completa, pueden operar con o sin transformador. Los diodos se enumeran en el orden de las secuencias de conducción, y cada uno conduce durante 120°. La secuencia de conducción para los diodos es D1-D2, D3-D2, D3-D4, D5-D6 y D1-D6. El par de diodos conectados entre el par de líneas de alimentación que tienen el mayor voltaje instantáneo de línea a línea es el que conduce. (Rashid, 2004).

**Figura 4.2.** Rectificador trifásico de puente completo. (Mohan, Undeland, & Robbins, 2009).

Parecido al análisis de rectificadores monofásicos de puente completo, empezaremos con circuitos sencillos antes de pasar al circuito ilustrado en la figura 4.2.

La corriente del rectificador fluye a través de un diodo del grupo superior y uno del grupo inferior. El diodo en el grupo superior con su ánodo en el potencial más alto conducirá, y los otros dos se vuelven de polarización inversa. (Mohan, Undeland, & Robbins, 2009).

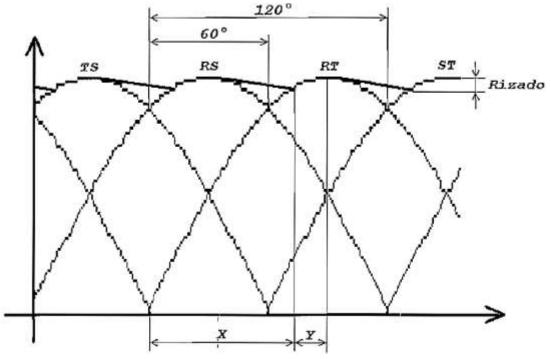

La forma de onda instantánea de  $v_d$  consiste en seis segmentos por ciclo de frecuencia de línea. Por ende, este rectificador a menudo se llama rectificador de seis impulsos. Cada segmento pertenece a una de las seis combinaciones de voltaje de línea a línea. Cada diodo conduce para 120°, como se muestra en la figura 4.3. La conmutación de corriente de un diodo al siguiente es instantánea, con base en la suposición de que  $L_s$  =0. Los diodos en la figura 5-31 están numerados de manera que conducen en la secuencia 1, 2, 3,... (Mohan, Undeland, & Robbins, 2009).

**Figura 4.3.** Formas de onda en el circuito de la figura 4.2. (Mohan, Undeland, & Robbins, 2009).

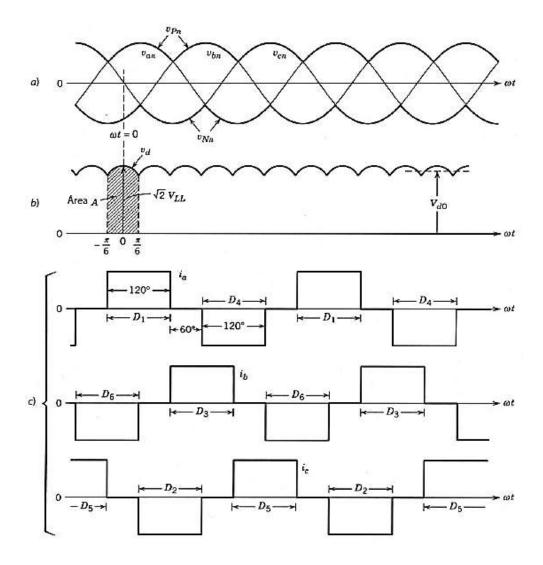

# 4.3 TRANSISTORES BIPOLARES DE PUERTA AISLADA (IGBT)

Un IGBT (del inglés, insulated gate bipolar transistor) tiene alta impedancia de entrada, como los MOSFET, y pocas pérdidas por conducción en estado activo, como los BJT. Sin embargo, no tiene problema de segunda avalancha, como los BJT. Por el diseño y la estructura del microcircuito, se controla la resistencia equivalente de drenaje a fuente, para que se comporte como la de un BJT. (Rashid, 2004).

El símbolo de circuito para un IGBT se muestra en la figura 4.4a, y sus características de *i-v*, en la figura 4.4b. Los IGBT tienen algunas de las ventajas de los MOSFET, BJT y GTO combinados. Parecido al MOSFET, el IGBT tiene una puerta de alta impedancia que sólo requiere una pequeña cantidad de energía para conmutar el

dispositivo. Igual que el BJT, el IGBT tiene un voltaje de estado activo pequeño, incluso en dispositivos con grandes voltajes nominales de bloqueo (por ejemplo, Venc es de 2 a 3 V en un dispositivo de 1000V). Parecidos al GTO, los IGBT se pueden diseñar para bloquear tensiones negativas, como lo indican sus características de conmutación idealizadas que se muestran en la figura 4.4c. (Mohan, Undeland, & Robbins, 2009).

**Figura 4.4.** Un IGBT: (a) símbolo, (b) característica de i-v, (c) características idealizadas. (Mohan, Undeland, & Robbins, 2009).

Para obtener un sistema eficiente es necesario que las pérdidas tanto dinámicas como estáticas del semiconductor sean las menores posibles, para cumplir con este propósito lo ideal es que el semiconductor se comporte como un interruptor. (Rashid, 2004), (Mohan, Undeland, & Robbins, 2009) y (Espinoza Torres, 2000).

Las pérdidas de potencia estáticas se presentan cuando el elemento se encuentra apagado o encendido. En el primer caso el elemento se encuentra en un estado abierto o de corte, en el cual, las pérdidas son función de la corriente de fuga y el voltaje aplicado entre sus terminales. En el segundo caso, el elemento se encuentra en un estado cerrado o de saturación en cuyo caso las pérdidas son función de la corriente que circule por el mismo y su voltaje de saturación. (Rashid, 2004), (Mohan, Undeland, & Robbins, 2009) y (Espinoza Torres, 2000).

De los tiempos de encendido y apagado (de corte a saturación) dependen en proporción directa las pérdidas de potencia dinámicas, por lo cual estas son propias de cada semiconductor. En la actualidad el semiconductor que presenta las mejores

características de las nombradas anteriormente son los IGBT's, los cuales se analizan brevemente a continuación (Rashid, 2004), (Mohan, Undeland, & Robbins, 2009) y (Espinoza Torres, 2000):

- Son elementos de tres terminales controlados por voltaje.

- Presentan elevada impedancia de entrada y una baja resistencia de salida típicamente menores que  $10m\Omega$  que le da un alto factor de amortiguamiento para cargas inductivas.

- Tienen áreas de operación segura (SOA) muy amplias.

- No presentan el fenómeno de avalancha térmica por poseer un coeficiente positivo de temperatura, es decir, que a medida que la temperatura se incrementa, contrarrestando así, la tendencia del aumento de la corriente lo que les permite trabajar a altas temperaturas sin fundirse.

- Facilidad de control al exigir pequeñas corrientes de entrada.

- Poseen una razonable tolerancia a picos de corriente.

- Se pueden conectar en paralelo para incrementar su capacidad de manejo de corriente.

- Poseen una alta ganancia de corriente.

- Son elementos de portadores minoritarios.

- Disipan menor calor que otro semiconductor bajo similares características.

- Son más rápidos que los BJT's.

- Poseen densidades de corriente más altas que los MOSFET's de potencia equivalente, esto hace que requieran de menores aéreas de pastillas y pueden manejar voltajes de salida más altos con muy bajas pérdidas.

- Puede integrar el diodo inverso entre sus terminales de salida, que es seleccionado según lo requiera el usuario.

Estas son las características más importantes de los IGBT's, por otro lado, entre sus desventajas podemos citar las siguientes (International Rectifier, 1997) y (Mohan, Undeland, & Robbins, 2009):

- Sus tiempos de conmutación son mayores a los que poseen los MOSFET's, pero las nuevas generaciones de IGBT's han mejorado las características.

- Al ser elementos de portadores minoritarios sus características de conducción tienden a degradarse con la temperatura, por lo cual se limitan a aplicaciones de baja y media frecuencia, siendo los MOSFET's de potencia los más adecuados y eficientes para estas aplicaciones.

Una clasificación para los IGBT's en función de su velocidad es (Mohan, Undeland, & Robbins, 2009) y (International Rectifier, 1997):

- Lentos.

- Rápidos.

- Ultra rápidos.

Cada uno de los cuales está optimizado para un rango de frecuencias.

Debido a la baja impedancia de entrada estos dispositivos son sensibles a daños por electricidad estática (ESD) al ser instalados inadecuadamente, por lo cual deben ser manipulados tomando todas las precauciones como es: no manipularlos más de lo necesario, mantenerlos guardados en su recipiente antiestático, durante la soldadura hacerlo con un cautín inalámbrico o desconectado de la red AC, entre otras. Parámetros como niveles bajos de humedad relativa (menores al 40%) así como la vecindad de campos eléctricos agravan el problema de la electricidad estática. (Espinoza Torres, 2000).

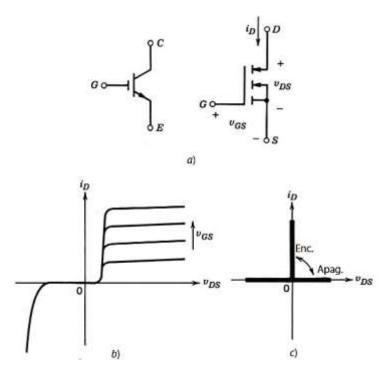

### 4.4 INVERSORES DE CC – CA DE MODO CONMUTADO: CC – CA SINUSOIDAL

Los inversores de CC a CA de modo conmutado se usan en motores de CA y fuentes de alimentación no interrumpibles, donde el objetico es producir una salida sinusoidal de CA cuya magnitud y frecuencia pueden controlarse. Como ejemplo, considere un motor de CA como el de la figura 4.3, en forma de un diagrama de bloques. El voltaje de CC se obtiene mediante la rectificación y filtrado del voltaje de línea, la mayoría de las veces por media de los circuitos rectificadores por diodos que se acabó de analizar. Si la carga de motor es de CA, como veremos más adelante, es deseable que el voltaje en sus terminales sea sinusoidal y ajustable en magnitud y frecuencia. Esto se logra por medio del inversor de CC a CA de modo conmutado de la figura 4.3, que acepta un

voltaje de CC como entrada y produce el voltaje de CA deseado. (Mohan, Undeland, & Robbins, 2009).

**Figura 4.4.** Inversor de modo conmutado en un motor de CA. (Mohan, Undeland, & Robbins, 2009).

Estos inversores se denominan inversores de fuente de voltaje (VSI). Los VSI se subdividen en las siguientes tres categorías:

- 1. Inversores modulados por ancho de pulsos.

- 2. Inversores de onda cuadrada.

- 3. Inversores monofásicos con cancelación de voltaje.

En este caso se tendrá en cuenta el primero debido a que es la tecnología a utilizar para el diseño del variador de frecuencia. Por lo tanto, se ampliará su concepto a continuación.

#### 4.4.1 INVERSORES MODULADOS POR ANCHO DE PULSOS

En estos inversores, el voltaje de CC de entrada es esencialmente de magnitud constante, como en el circuito de la figura 4.3, donde se usa un rectificador de diodos para rectificar el voltaje de línea. Por tanto, el inversor debe controlar la magnitud y la frecuencia de los voltajes de CA de salida. Esto se logra mediante PWM de los interruptores del inversor, por ende, estos inversores se llaman inversores PWM. Hay varios métodos para modular los interruptores del inversor por ancho de pulsos a fin de formar los voltajes de CA de salida, de modo que sean lo más parecido posible a una onda sinusoidal. De estos diferentes métodos de PWM se analizará en detalle uno llamado PWM sinusoidal. (Mohan, Undeland, & Robbins, 2009).

Los inversores se pueden clasificar en el sentido amplio en dos tipos: 1) inversores monofásicos y 2) inversores trifásicos. Cada uno puede usar dispositivos controlados de encendido y apagado (como transistores bipolares de unión [BJT], transistores de efecto de campo de metal óxido semiconductor [MOSFET], transistores bipolares de compuerta

aislada [IGBT], tiristores controlados por compuerta [GTO]). Estos usan en general señales de control por modulación por ancho de pulso (PWM) para producir un voltaje de salida de CA. (Rashid, 2004).

### 4.5 INVERSORES TRIFÁSICOS

En aplicaciones como fuentes de alimentación no interrumpibles y motores de CA, los inversores trifásicos son comunes para alimentar cargas trifásicas. El circuito de un inversor trifásico más frecuente consiste en tres patas o terminales, una para cada fase, como se muestra en la figura 4.4. La salida de cada pin, por ejemplo,  $v_{AN}$  depende únicamente de  $V_d$  y el estatus del interruptor; el voltaje de salida es independiente de la corriente de la carga de salida, pues uno de los dos interruptores en una pata siempre está encendido en algún instante. (Mohan, Undeland, & Robbins, 2009).

Figura 4.4. Inversor trifásico. (Mohan, Undeland, & Robbins, 2009).

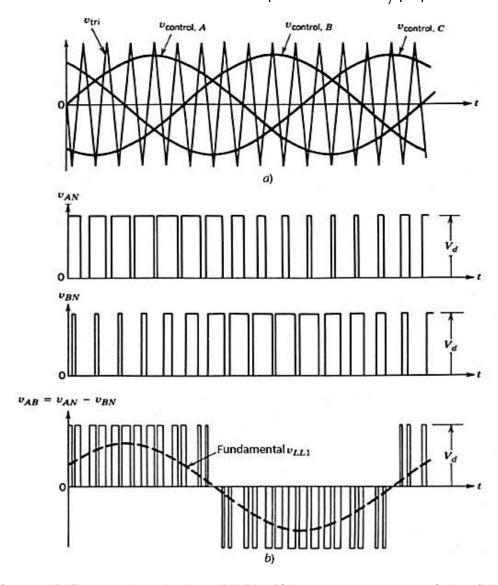

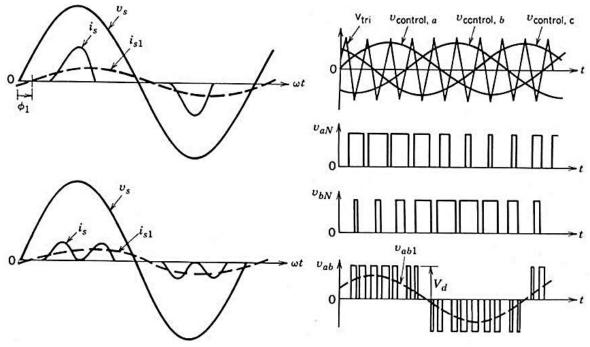

### 4.5.1 PWM EN INVERSORES TRIFÁSICOS DE FUENTES DE VOLTAJE

Parecido a los inversores monofásicos, el objetivo en inversores trifásicos modulados por el ancho de pulsos es formar y controlar los voltajes de salida trifásicos en magnitud y frecuencia por medio de un voltaje de entrada esencialmente constante  $V_d$ . A fin de obtener voltajes de salida trifásicos equilibrados en un inversor trifásico de PWM, se compara la misma forma de onda de voltaje triangular con tres voltajes de control sinusoidales que están 120° fuera de fase, como se muestra en la figura 4.5a.

Observe también que, según la figura 4.5b, una cantidad idéntica del componente medio de CC está presente en los voltajes de salida  $v_{AN}$  y  $v_{BN}$ , los cuales se miden respecto del bus de CC negativo. Estos componentes de CC se cancelan en los voltajes de línea a

línea, por ejemplo, en  $v_{AB}$  que se muestra en la figura 4.5b. (Mohan, Undeland, & Robbins, 2009).

Las consideraciones de PWM se resumen de la siguiente manera:

- 1. **Para valores bajos de**  $m_f$ : A fin de eliminar los armónicos pares, se debe usar un PWM sincronizado y  $m_f$  debe ser un entero impar. Además,  $m_f$  debe ser un múltiplo de 3 para cancelar los armónicos más dominantes en el voltaje de línea a línea.

- 2. Para valores grandes de  $m_f$ : Aplican los comentarios en la sección 8-2-1-2 para un PWM monofásico.

- 3. **Durante una sobremodulación (m\_a > 1.0):** Sin tener en cuenta el valor de  $m_f$ , se deben observar las condiciones correspondientes a un  $m_f$  pequeño.

**Figura 4.5.** Formas de onda de un PWM trifásico y su espectro armónico. (Mohan, Undeland, & Robbins, 2009).

En la región de sobremodulación, comparada con la región lineal ( $m_a \leq 1.0$ ), aparecen más armónicos de banda lateral centrados alrededor de las frecuencias de los armónicos  $m_f$  y sus múltiplos. Sin embargo, tal vez los armónicos dominantes no tengan una amplitud tan grande como en la parte lineal. Por tanto, la pérdida de potencia en la carga debida a las frecuencias armónicas posiblemente no sea tan alta en la región de sobremodulación como lo sugiere la presencia de adicionales armónicos de banda lateral. Según la naturaleza de la carga y la frecuencia de modulación, las pérdidas debidas a estos armónicos en sobremodulación podrán ser incluso menores que aquellas en la región lineal del PWM. Además, para valores grandes de  $m_f$ , la ondulación de la corriente en el inversor PWM será considerablemente más baja en comparación con un inversor de ondas cuadradas. (Mohan, Undeland, & Robbins, 2009).

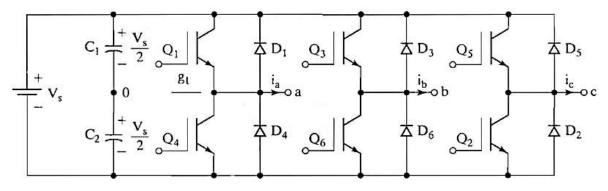

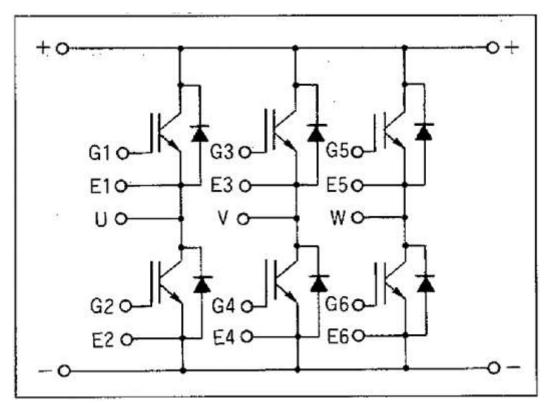

#### 4.5.2 CONDUCCIÓN DEL INVERSOR TRIFÁSICO

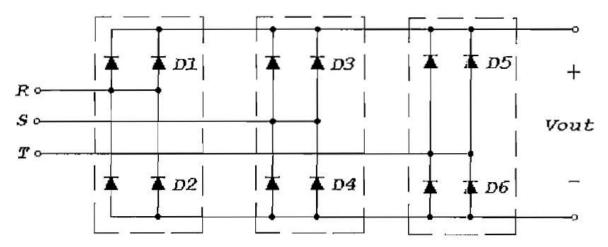

Se puede obtener una salida trifásica con una configuración de seis transistores y seis diodos, como se ve en la figura 4.6 que es otra forma de dibujar el circuito del inversor de la figura 4.4. Se pueden aplicar dos clases de señales de control a los transistores: conducción a 180° o conducción a 120°. La conducción a 180° utiliza mejor los interruptores, y es el método que se prefiere. (Rashid, 2004).

Figura 4.6. Puente inversor trifásico. (Rashid, 2004).

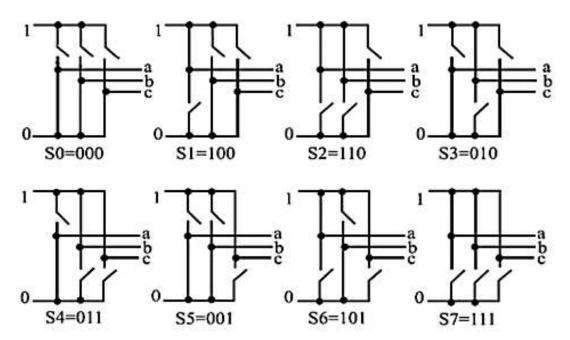

La tabla 1 muestra ocho estados de conmutación. Los transistores Q1 y Q6 de la figura 4.6 actúan como los interruptores Si y S6, respectivamente. Si dos interruptores, uno superior y uno inferior, conducen al mismo tiempo de tal modo que el voltaje de salida sea  $\pm Vs$ , el estado de conmutación es 1, mientras que, si esos interruptores están abiertos al mismo tiempo, el estado de conmutación es 0. Los estados de 1 a 6 producen voltajes de salida distintos de cero. Los estados 7 y 8 producen voltajes de línea cero, y las corrientes de línea pasan libremente a través de los diodos superior o inferior de corrida libre. (Rashid, 2004).

Para generar determinada forma de onda de voltaje, el inversor pasa de un estado a otro. Así, los voltajes de línea de salida de CA que resultan están formados por valores discretos de voltajes Vs, 0 y -Vs'. Para generar determinada forma de onda, la selección

de los estados se suele hacer con una técnica de modulación que asegure sólo el uso de los estados válidos. (Rashid, 2004).

Más adelante se ampliará acerca de las diferentes técnicas de modulación PWM que se pueden implementar en un inversor trifásico.

| Estado                                                     | Estado<br>no. | Estados de interruptor | U <sub>ab</sub> | U <sub>bc</sub> | U <sub>ca</sub> | Vector espacial                                   |

|------------------------------------------------------------|---------------|------------------------|-----------------|-----------------|-----------------|---------------------------------------------------|

| S1, S2 y S6 están cerrados y S4,<br>S5 y S3 están abiertos | 1             | 100                    | Vs              | 0               | -Vs             | $V_1 = 1 + j0.577 = 2/\sqrt{3} \angle 30^\circ$   |

| S2, S3 y S1 están cerrados y S5,<br>S6 y S4 están abiertos | 2             | 110                    | 0               | Vs              | -Vs             | <b>V</b> <sub>2</sub> = j1.155 = 2/√3 ∠90°        |

| S3, S4 y S2 están cerrados y S6,<br>S1 y S5 están abiertos | 3             | 010                    | -Vs             | Vs              | 0               | $V_3 = -1 + j0.577 = 2/\sqrt{3} \angle 150^\circ$ |

| S4, S5 y S3 están cerrados y S1,<br>S2 y S6 están abiertos | 4             | 011                    | -Vs             | 0               | Vs              | <b>V</b> <sub>4</sub> = -1 -j0.577 = 2/√3 ∠210°   |

| S5, S6 y S4 están cerrados y S2,<br>S3 y S1 están abiertos | 5             | 001                    | 0               | -Vs             | Vs              | $V_5 = -j1.155 = 2/\sqrt{3} \angle 270^\circ$     |

| S6, S1 y S5 están cerrados y S3,<br>S4 y S2 están abiertos | 6             | 101                    | Vs              | -Vs             | 0               | $V_6 = 1 - j1.155 = 2/\sqrt{3} \angle 330^\circ$  |

| S1, S3 y S5 están cerrados y S4,<br>S6 y S2 están abiertos | 7             | 111                    | 0               | 0               | 0               | <b>V</b> <sub>7</sub> = 0                         |

| S4, S6 y S2 están cerrados y S1,<br>S3 y S5 están abiertos | 8             | 000                    | 0               | 0               | 0               | <b>V</b> <sub>0</sub> = 0                         |

Tabla 4.1. Estados de interruptor para inversor trifásico de fuente de voltaje VSI.

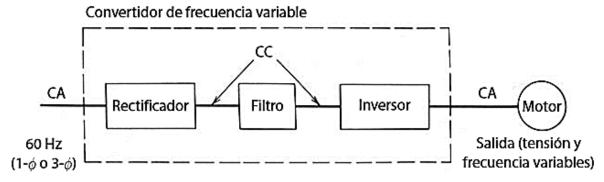

#### 4.6 CONVERTIDORES DE FRECUENCIA VARIABLE

Los accionamientos de frecuencia variable usan inversores con una entrada de CC, como ya vimos. La figura 4.7 ilustra el concepto básico donde la entrada del sistema de suministro de energía se convierte en CC por medio de un rectificador controlado o no controlado y luego se invierte para proveer tensiones y corrientes trifásicas al motor con magnitud y frecuencia ajustables. (Mohan, Undeland, & Robbins, 2009).

Figura 4.7. Convertidor de frecuencia variable. (Mohan, Undeland, & Robbins, 2009).

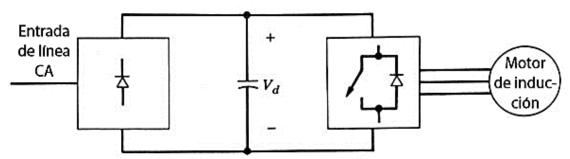

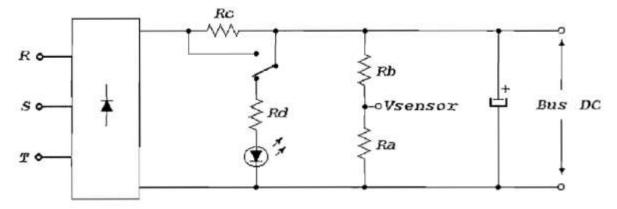

La figura 4.8 muestra el esquema de un PWM-VSI con un rectificador de diodos. VSI o VFI implica que la entrada de CC aparece como fuente de tensión de CC (idealmente sin impedancia interna) al inversor. Por otro lado, en el CSI, la entrada de CC aparece como fuente de corriente CC al inversor. En los controladores VSI se usa un capacitor grande para que la entrada al inversor aparezca como fuente de tensión con una impedancia interna muy pequeña en la frecuencia de conmutación del inversor. (Mohan, Undeland, & Robbins, 2009).

**Figura 4.8.** PWM.VSI con un rectificador de diodos. (Mohan, Undeland, & Robbins, 2009).

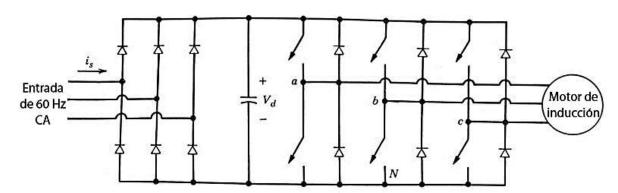

#### 4.6.1 ACCIONAMIENTOS PWM-VSI DE FRECUENCIA VARIABLE

La figura 4.9 muestra el esquema de un accionamiento PWM-VSI suponiendo una entrada del sistema de suministro de energía trifásica. Como un breve repaso de lo que ya vimos, un inversor PWM controla tanto la frecuencia como la magnitud de salida de tensión. Por tanto, se usa por lo general un rectificador no controlado de puente de diodos. Un posible método para generar las señales de control de los interruptores del inversor es comparar tres tensiones sinusoidales de control (en la frecuencia de salida deseada y proporcional a la magnitud de tensión de salida) con una forma de onda triangular en una frecuencia de conmutación seleccionada, como se muestra en la figura 4.9. (Mohan, Undeland, & Robbins, 2009).

**Figura 4.9.** Esquema de un accionamiento PWM-VSI. (Mohan, Undeland, & Robbins, 2009).

Los armónicos en la tensión de salida de un inversor PWM aparecen como bandas laterales de la frecuencia de conmutación y sus múltiplos. Por consiguiente, una frecuencia de conmutación alta produce una corriente en esencia sinusoidal (más un pequeño rizo sobreimpuesto en caso de frecuencia alta) en el motor. (Mohan, Undeland, & Robbins, 2009).

**Figura 4.10.** Formas de onda de un accionamiento PWM-VSI. (Mohan, Undeland, & Robbins, 2009).

Como la corriente del rizo a través del capacitor CC del bus está en la frecuencia de conmutación, la impedancia de la fuente de CC de entrada vista por el inversor sería más pequeña con frecuencias de conmutación más altas. Por tanto, basta un valor pequeño de capacitancia en inversores de PWM, pero este capacitor debe ser capaz de transportar la corriente de rizo. Una capacitancia pequeña a través del rectificador de diodos también permite una mejor forma de onda de la corriente de entrada tomada del sistema de suministro de energía. Sin embargo, se debe poner atención para que no se permita que el rizo de tensión en la tensión del bus de CC crezca demasiado, pues esto causaría armónicos adicionales en la tensión que se aplica al motor. (Mohan, Undeland, & Robbins, 2009).

### 4.6.2 IMPACTO DE LOS ARMÓNICOS DE PWM-VSI

Como los armónicos están en una frecuencia alta en la tensión de salida de un inversor PWM, el rizo en la corriente del motor suele ser pequeño, debido a las altas reactancias de dispersión en estas frecuencias. Debido a que estos armónicos de tensión

de altas frecuencias tienen una amplitud igual o incluso más alta en comparación con el componente de frecuencia fundamental, son predominantes las pérdidas en el hierro (corrientes parásitas e histéresis en el estator y el hierro del rotor). De hecho, las pérdidas totales debido a armónicos pueden ser aún más altas con un inversor PWM que con uno de onda cuadrada. Esta comparación dependería por supuesto del diseño del motor, de la propiedad del material magnético y de la frecuencia de conmutación. Debido a estas pérdidas adicionales por armónicos se recomienda por lo general que se use un motor estándar con una potencia especificada de 5 a 10% más alta. (Mohan, Undeland, & Robbins, 2009).

# 4.7 FUNDAMENTOS DE LA MODULACIÓN PULSE WIDTH MODULATION (PWM)

### 4.7.1 MODULACIÓN PWM BASADA EN PORTADORA (CB-PWM)

Los interruptores superiores del VSI se activan en los instantes en que se igualan las amplitudes de portadora y moduladora. Existen dos métodos para obtener la amplitud de la moduladora: a) PWM natural y b) PWM regular.

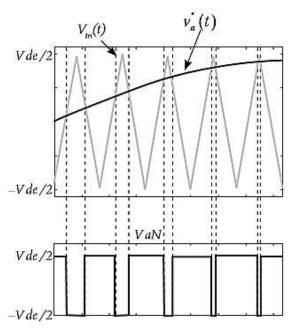

En el PWM natural, la conmutación ocurre durante la intersección instantánea entre moduladora y portadora como se ilustra en la figura 4.11. Al emplear el PWM natural, los centros de los pulsos generados no quedan alineados con los picos de la señal triangular lo que provoca asimetría en los pulsos resultantes. (Camacho, López, Díaz, & Gaviria, 2012).

**Figura 4.11.** Proceso de generación del tren de pulsos en PWM de muestreo natural. (Camacho, López, Díaz, & Gaviria, 2012).

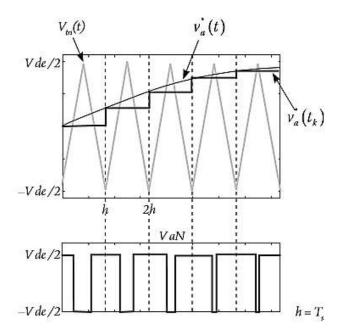

En el caso de la PWM regular, la amplitud de referencia se obtiene a partir del muestreo de la señal moduladora en el instante del pico negativo o positivo de la portadora (Svensson, 1999). La figura 4.12 presenta el caso de muestreo en el pico negativo de la portadora, note que esta configuración provoca que el eje de simetría de la señal triangular coincida con el eje de simetría del pulso generado. Por esta razón, este caso de la modulación regular recibe el nombre de **PWM regular simétrico**. (Camacho, López, Díaz, & Gaviria, 2012).

**Figura 4.12.** Proceso de generación del tren de pulsos en PWM regular simétrico. (Camacho, López, Díaz, & Gaviria, 2012).

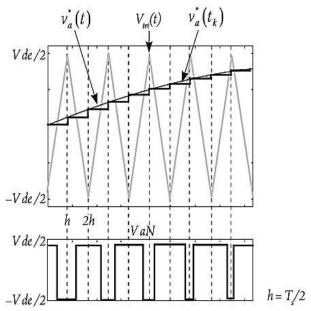

Cuando el muestreo de la moduladora se realiza en los instantes de los picos negativos y positivos de la portadora, los flancos de bajada y los de subida son determinados empleando muestras diferentes de la moduladora. En este caso se genera un tren de pulsos asimétrico, como se muestra en la figura 4.13. Este método recibe el nombre de **PWM regular asimétrico**. (Camacho, López, Díaz, & Gaviria, 2012)

**Figura 4.13.** Proceso de generación del tren de pulsos en PWM regular asimétrico. (Camacho, López, Díaz, & Gaviria, 2012).

En comparación con la PWM natural, la PWM regular es más apropiada para implementaciones digitales puesto que en sus dos enfoques (simétrico y asimétrico) los instantes de subida y bajada de los flancos pueden ser calculados en tiempo real empleando ecuaciones algebraicas sencillas (Pardo & Díaz, 2004). Adicionalmente, el PWM simétrico se caracteriza por generar un bajo contenido armónico en el voltaje de salida del inversor, siendo comparativamente superior el producido por el PWM asimétrico (Holmes, 1998; Moynihan, 1998).

De estos métodos se destacan diez desarrollos (Hava, 1998) que pueden ser clasificados en tres grupos: a) continuos, b) discontinuos, c) híbridos. A continuación, se expondrán algunas características de estos dos grupos de moduladores:

### 4.8 MÉTODOS PWM CONTINUOS (CPWM)

Estos métodos se caracterizan porque en cada ciclo de portadora generan al menos una conmutación. Hacen parte de esta clasificación: la PWM sinusoidal (SPWM), los métodos con inyección del tercer armónico (THIPWM) y la PWM con vectores espaciales basada en portadora (CB-SVPWM). (Camacho, López, Díaz, & Gaviria, 2012).

### 4.8.1 LA MODULACIÓN PWM SINUSOIDAL (SPWM)

En la SPWM introducida por Schönung (1964), las señales moduladoras conforman un conjunto trifásico sinusoidal balanceado que configura la amplitud, frecuencia y fase a la salida del inversor. En la ecuación 4.1 se presenta la definición algebraica de las moduladoras en SPWM, donde A es la amplitud máxima de las moduladoras y  $\omega_m$  su frecuencia angular. (Camacho, López, Díaz, & Gaviria, 2012).

$$V_{a}(t) = Asin(\omega_{m}t)$$

$$V_{b}(t) = Asin\left(\omega_{m}t - \frac{2\pi}{3}\right)$$

$$V_{c}(t) = Asin\left(\omega_{m}t - \frac{4\pi}{3}\right)$$

$$V_{a}(t) + V_{b}(t) + V_{c}(t) = 0$$

$$(4.1)$$

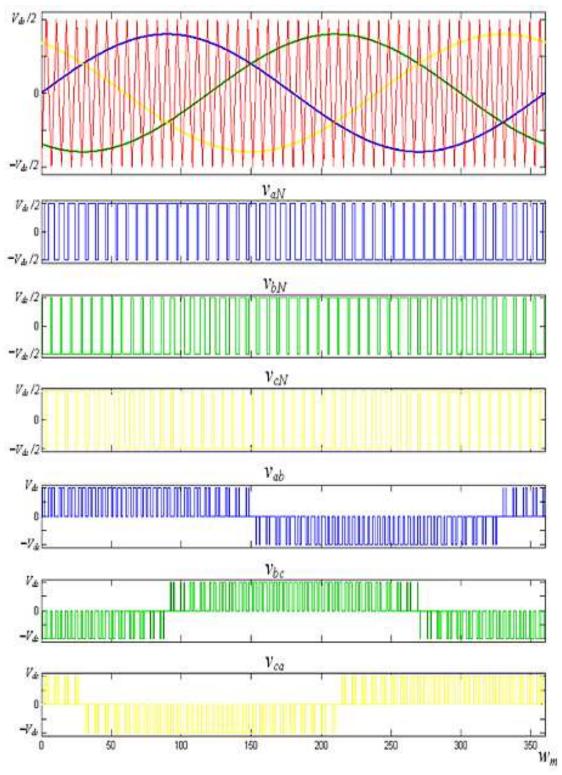

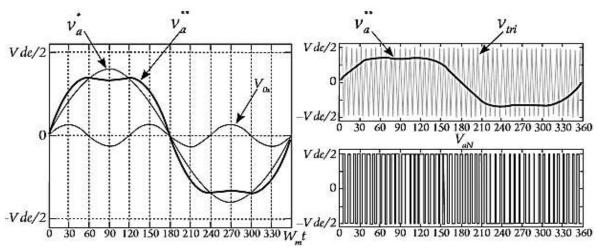

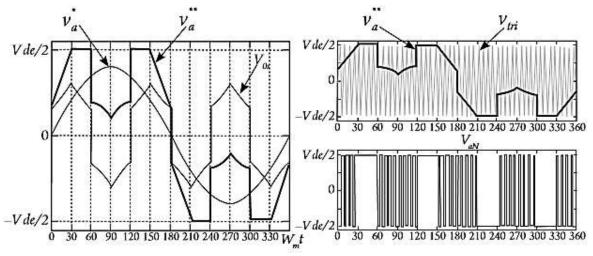

La figura 4.14 presenta el proceso de modulación SPWM basado en portadora para las fases  $v_{aN}$ ,  $v_{bN}$ ,  $v_{cN}$  junto con los voltajes línea a línea resultantes. En general, la PWM sinusoidal o SPWM es una técnica simple que garantiza buenos resultados en todas las condiciones de trabajo, incluida la sobremodulación y que presenta un buen desempeño armónico.

Este buen desempeño se debe a su frecuencia de conmutación constante, que genera un espectro definido, con componentes en alta frecuencia y con reducción de armónicos de bajo orden. (Pardo & Díaz, 2004).

Debido a lo anterior, las primeras versiones del método tuvieron gran aceptación en la industria, sin embargo, rápidamente se evidenció que la limitación en su rango lineal provocaba que los motores trabajaran con tensiones inferiores a las nominales, reduciendo así su desempeño (Bergas, 2000).

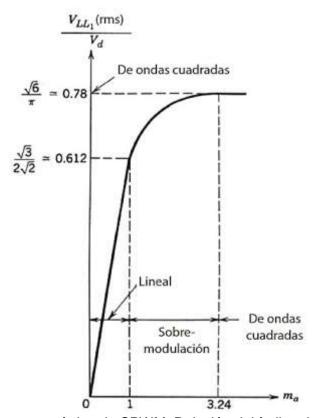

El rango lineal de modulación se puede expresar mediante el máximo índice de modulación dentro de zona lineal, en el caso del modulador SPWM este corresponde a  $M_{lineal\ m\acute{a}x}=1$ . Este rango se muestra en la figura 4.15. (Camacho, López, Díaz, & Gaviria, 2012).

**Figura 4.14.** Proceso de modulación SPWM trifásico. (Camacho, López, Díaz, & Gaviria, 2012).

**Figura 4.15.** Curva característica de SPWM. Relación del índice de modulación con el porcentaje de utilización del bus DC. (Malinowski, 2001) y (Mohan, Undeland, & Robbins, 2009).

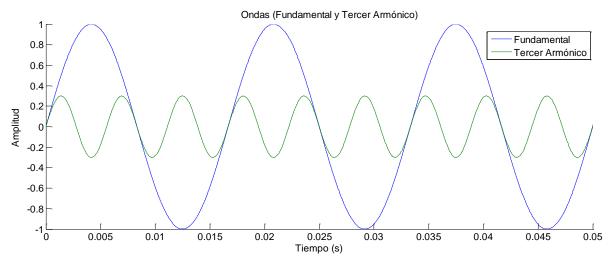

## 4.8.2 INYECCIÓN DEL TERCER ARMÓNICO (THIRD HARMONIC INJECTION PWM [THIPWM])

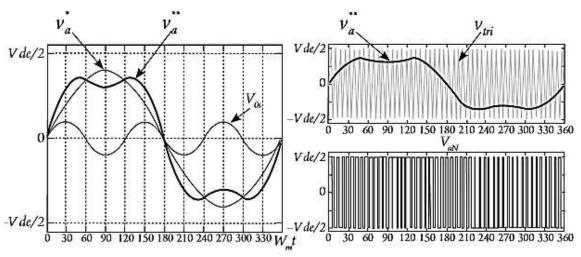

Estos métodos logran incrementar la tensión trifásica de salida del inversor hasta en un 15% sin salir de zona lineal (90,7 % del voltaje Six-Step). En 1975, Buja propone inyectar una señal de secuencia cero con amplitud 1/6 de la señal fundamental y el triple de la frecuencia fundamental (Buja e Indri, 1975). Este método es conocido como THIPWM1/6, su señal de secuencia cero se presenta en la figura 4.16 y en la ecuación 4.2. (Camacho, López, Díaz, & Gaviria, 2012).

$$V_{0s}(t) = \frac{A}{6}\sin(3\omega_m t) \tag{4.2}$$

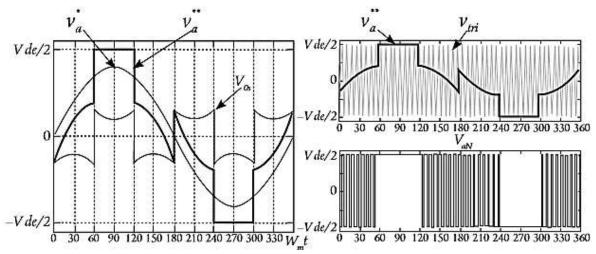

Como se muestra en la figura 4.16, la señal moduladora  $V_a^{**}$  es el resultado de la suma de dos señales sinusoidales. Note que en los rangos donde la fundamental  $V_a^*$  alcanza su máxima amplitud ([ $60^\circ \le \omega_m t \le 120^\circ$ ] y [ $240^\circ \le \omega_m t \le 300^\circ$ ]), la amplitud de la nueva señal  $V_a^{**}$  se reduce. Esta reducción es compensada en los primeros  $60^\circ$  y en los últimos  $60^\circ$  de cada medio periodo de fundamental permitiendo el uso de índices de modulación mayores a la unidad sin pasar a sobremodulación. (Camacho, López, Díaz, & Gaviria, 2012).

**Figura 4.16.** THIPWM1/6. Generación de la señal y modulación de la fase *a*. (Camacho, López, Díaz, & Gaviria, 2012).

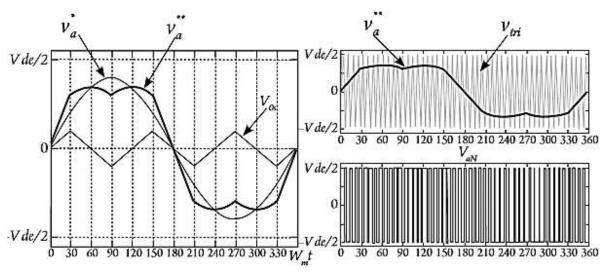

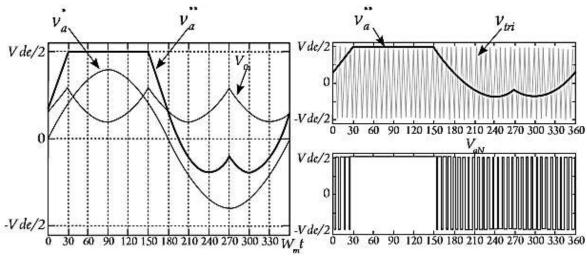

En 1986, Bowes calcula una moduladora de mínima distorsión armónica, concluyendo como valor óptimo la inyección del tercer armónico con amplitud 1/4 de la fundamental (Bowes y Midoun, 1986). En la actualidad, dicho método es conocido como THIPWM1/4; su señal de secuencia cero se expresa en la ecuación 4.3. Este método permite un rango lineal menor al presentado por THIPWM1/6 ( $M_{lineal\ m\acute{a}x}=1.117$ ) pero a cambio, presenta una mejora en el espectro armónico del tren de pulsos resultante. Las formas de onda correspondientes a THIPWM1/4 se ilustran en la figura 4.17. (Camacho, López, Díaz, & Gaviria, 2012).

$$V_{0s}(t) = \frac{A}{4} \sin(3\omega_m t) \tag{4.3}$$

Los dos moduladores THIPWM presentan complejidad en la implementación ya que el cálculo de la señal de frecuencia triple involucra altos requerimientos computacionales (Hava, 1998). Por esta razón su popularidad no alcanzó ambientes industriales y solo perdura en los académicos. (Camacho, López, Díaz, & Gaviria, 2012).

**Figura 4.17.** THIPWM1/4. Generación de la señal y modulación de la fase *a.* (Camacho, López, Díaz, & Gaviria, 2012).

# 4.8.3 PWM CON VECTORES ESPACIALES BASADA EN PORTADORA (CARRIER-BASED SPACE-VECTOR-PWM [CB-SVPWM])

Este esquema conocido en la actualidad como CB-SVPWM, es atribuido a King (1974). Para la generación de la señal de secuencia cero este modulador emplea la expresión en la ecuación 4.4. (Camacho, López, Díaz, & Gaviria, 2012).

$$V_{0s}(t) = -0.5[m\acute{a}x(V_a^*, V_b^*, V_c^*) + m\acute{n}(V_a^*, V_b^*, V_c^*)]$$

(4.4)

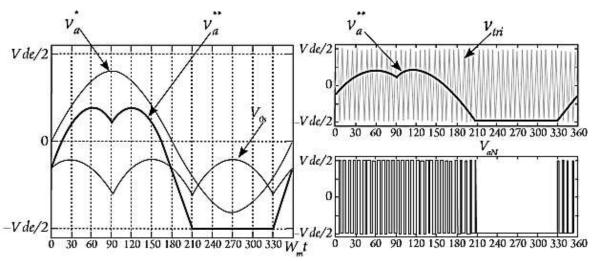

Es decir, compara la magnitud de las señales fundamentales  $V_i^*(t)$ , para realizar dos selecciones: a) la señal con mínima magnitud y b) la señal de máxima magnitud; posteriormente suma las selecciones y escala el resultado con un factor de -0.5. El resultado de la señal de secuencia cero es una señal triangular, periódica, con el triple de la frecuencia fundamental y 1/4 de amplitud fundamental como se ilustra en la figura 4.18. Este algoritmo es posiblemente el método PWM de inyección de señal de secuencia cero más antiguo reportado en la literatura. Una década después reapareció empleando la teoría de vectores espaciales y bajo una implementación digital, de aquí su nombre. (Rodríguez Cortés, 2005) y (Camacho, López, Díaz, & Gaviria, 2012).

**Figura 4.18.** CB-SVPWM. Generación de la señal y modulación de la fase *a*. (Camacho, López, Díaz, & Gaviria, 2012).

# 4.9 MÉTODOS PWM DISCONTINUOS (DISCONTINUOUS PULSE WIDTH MODULATION [DPWM])

Los DPWM generan conmutaciones solo en 2/3 del ciclo de la moduladora. Esto se logra inyectando una señal de secuencia cero que lleva a una de las tres señales fundamentales  $V_i^*(t)$  al nivel del pico positivo o negativo de la portadora triangular. Para elegir la fase que será saturada se aplican reglas de selección sobre las señales fundamentales; la fase seleccionada determina la forma de la señal de secuencia cero como se indica en la ecuación 4.5.

$$V_{0s}(t) = \text{sign}(V_x^*(t)) \frac{Vdc}{2} - V_x(t)$$

(4.5)

El subíndice x en la ecuación 4.5 corresponde al índice de fase que fue escogido con la regla de selección. Estas reglas son únicas para cada modulador y determinan la señal de secuencia cero de cada método de modulación discontinuo. Entre los métodos reportados se destacan ocho denominados: DPWM1, DPWMMax, DPWM2, DPWM0, DPWM3, DPWMMin, Generalized Discontinuous PWM (GDPWM) y Hybrid Discontinuous PWM (HDPWM) (Hava, 1998; López M., Camacho M., Díaz C., Gaviria L., y Bolaños, 2009). Estos métodos presentan un buen desempeño armónico en zona lineal y permiten un rango de modulación lineal máximo del 90,7% del voltaje six-step; a continuación, se realiza una breve descripción de cada uno de ellos. el análisis se limitará a las señales correspondientes a la fase a puesto que las señales de las fases b y c presentan la misma forma, pero desfasadas  $-120^{\circ}$  y  $-240^{\circ}$  respectivamente.

### 4.9.1 DPWM1

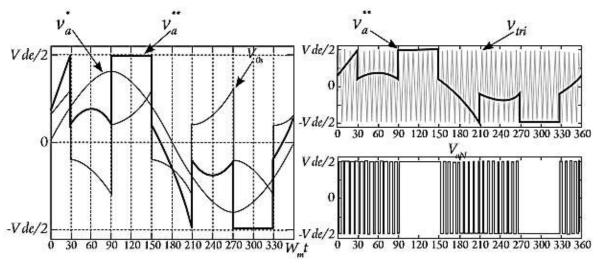

La primera versión de este método es reportada en (Depenbrock, 1977), donde emplean un rectificador de puente de diodos para generar una señal de secuencia cero, tal que sean reducidas las pérdidas por conmutación en aplicaciones con cargas de factor de potencia cercano a la unidad. En este método se selecciona la señal con mayor valor absoluto de entre las tres fundamentales; la señal seleccionada se lleva hasta el valor máximo positivo o negativo del bus DC durante 1/3 del ciclo de la fundamental (figuras 4.19 y 4.20). La regla de selección se indica en la ecuación 4.6.

$$IF(|V_a^*| \ge |V_b^*| \ AND \ |V_a^*| \ge |V_c^*|) \to V_{0s} = \text{sign}(V_a^*) \frac{Vdc}{2} - V_a$$

(4.6)

La señal  $V_{0s}$  generada se caracteriza por ser periódica con el triple de la frecuencia fundamental y discontinua. en la figura 4.19 se muestra que la moduladora resultante ( $V_a^{**}$ ) tiene dos instantes de saturación, ambos alrededor de los picos de la señal  $V_a^*$  y cada uno con una duración de 60°. En la figura 4.19, el tren de pulsos resultante indica que durante los primeros 60° de saturación, el interruptor inferior de la fase a, permanece abierto mientras el superior permanece cerrado, en tanto que durante los últimos 60° de saturación los estados se invierten; en consecuencia, la reducción en el número de conmutaciones es igual en los conmutadores inferiores y superiores de cada rama del inversor. (Camacho, López, Díaz, & Gaviria, 2012).

**Figura 4.19.** DPWM1. Generación de la señal y modulación de la fase *a*. (Camacho, López, Díaz, & Gaviria, 2012).

#### 4.9.2 DPWMMax

Este modulador fue reportado en (Taniguchi, Ogino e Irie, 1988) y busca saturar la fase de mayor valor instantáneo de entre las tres señales fundamentales. La regla de selección se indica en la ecuación 4.7.

$$IF (V_a^* \ge V_b^* AND V_a^* \ge V_c^*) \to V_{0s} = \text{sign}(V_a^*) \frac{Vdc}{2} - V_a$$

(4.7)

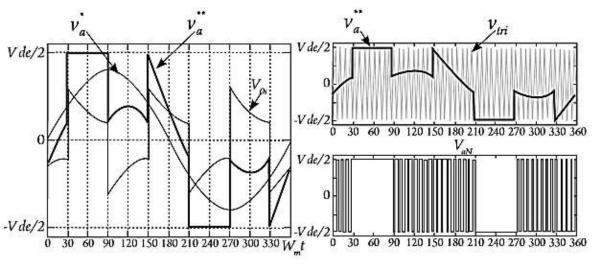

Como se indica en la figura 4.20, la zona de saturación está centrada en el máximo positivo de la señal  $V_a^*(t)$  y tiene una duración de 120°. El efecto de esta saturación se ilustra en la figura 4.19 donde se aprecia cómo, durante el rango  $[30^\circ \le \omega_m t \le 150^\circ]$  el conmutador superior de la fase a, permanece cerrado mientras el conmutador inferior permanece abierto; por tanto, con este algoritmo se genera una mayor reducción de pérdidas en los conmutadores inferiores. (Camacho, López, Díaz, & Gaviria, 2012).

**Figura 4.20.** DPWMMax. Generación de la señal y modulación de la fase *a*. (Camacho, López, Díaz, & Gaviria, 2012).

### 4.9.3 DPWM2

Ogasawara, Akagi y Nabae, 1989. Proponen una señal de secuencia cero que permita eliminar las conmutaciones en 30° de atraso, con respecto al pico del voltaje. Esta estrategia diseñada para cargas con ángulo de factor de potencia cercano a los 30° en atraso, busca evitar la conmutación cuando la corriente en los conmutadores presenta su valor más elevado. En este método las tres señales moduladoras  $V_a^*$ ,  $V_b^*$ ,  $V_c^*$  son atrasadas 30° y de las tres nuevas señales:  $V_{ax}^*$ ,  $V_{bx}^*$ ,  $V_{cx}^*$  se selecciona la de mayor magnitud. La señal seleccionada se satura, como en el caso de la DPWM1. Las formas de onda resultantes son indicadas en la figura 4.21 y la regla de selección es presentada en la ecuación 4.8. (Camacho, López, Díaz, & Gaviria, 2012).

IF

$$(V_a^* \ge V_b^* AND V_a^* \ge V_c^*) \to V_{0s} = \text{sign}(V_a^*) \frac{Vdc}{2} - V_a$$

(4.8)

**Figura 4.21.** DPWM2. Generación de la señal y modulación de la fase *a*. (Camacho, López, Díaz, & Gaviria, 2012).

### 4.9.4 DPWM0

En (Kenjo, 1990) desarrollan un modulador similar al presentado en (Ogasawara, 1989), pero dirigido a aplicaciones con cargas de factor de potencia en adelanto de 30°; este modulador es conocido como DPWM0. Para la generación de la señal de secuencia cero, las señales fundamentales  $V_a^*$ ,  $V_b^*$ ,  $V_c^*$  son desfasadas con adelanto de 30° originando tres nuevas señales:  $V_{ax}^*$ ,  $V_{bx}^*$ ,  $V_{cx}^*$ . Como en DPWM2, la señal de mayor magnitud absoluta es seleccionada y saturada (ver ecuación 4.8). Las formas de onda generadas son ilustradas en la figura 4.22.

**Figura 4.22.** DPWM0. Generación de la señal y modulación de la fase *a*. (Camacho, López, Díaz, & Gaviria, 2012).

### 4.9.5 DPWM3

Este modulador propuesto por Kolar, Ertl y Zach (1990) busca saturar la fase que presenta la amplitud con valor absoluto intermedio de las tres señales fundamentales. La regla de selección se resume en la ecuación 4.9 y las formas de onda generadas son presentadas en la figura 4.23. Entre las técnicas discontinuas ésta se caracteriza por ser la más efectiva en la reducción del contenido armónico (Narayanan, 1999).

$$IF(|V_b^*| \ge |V_a^*| \ge |V_c^*| OR|V_c^*| \ge |V_a^*| \ge |V_b^*|) \to V_{0s} = \text{sign}(V_a^*) \frac{Vdc}{2} - V_a$$

(4.9)

Como se ilustra en la figura 4.23, la señal moduladora discontinua  $V_a^{**}(t)$  presenta cuatro zonas de saturación, cada una de 30°, con sus centros alejados 45° del máximo de la señal  $V_a^*(t)$ . Esta división permite un incremento en el rango de aplicaciones, cubriendo cargas con ángulo de factor de potencia entre [–30°, 30°], a cambio de un incremento en pérdidas por conmutación. (Camacho, López, Díaz, & Gaviria, 2012).

**Figura 4.23.** DPWM3. Generación de la señal y modulación de la fase *a*. (Camacho, López, Díaz, & Gaviria, 2012).

#### 4.9.6 DPWMMin

Este modulador, propuesto también por Kolar (1990), es similar al DPWMMax, con la particularidad de que busca saturar la fase de menor valor instantáneo de entre las tres señales fundamentales. La regla de selección es resumida en la ecuación 4.10.

$$IF (V_a^* \le V_b^* AND V_a^* \le V_c^*) \to V_{0s} = \text{sign}(V_a^*) \frac{V_{dc}}{2} - V_a$$

(4.10)

Las formas de onda generadas son ilustradas en la figura 4.24. El desempeño de este método es similar al DPWMMax, con la diferencia que los interruptores superiores del inversor tienen pérdidas por conducción más bajas que los interruptores inferiores.

**Figura 4.24.** DPWMMin. Generación de la señal y modulación de la fase *a*. (Camacho, López, Díaz, & Gaviria, 2012).

## 4.10 MÉTODOS DPWM HÍBRIDOS

Estos métodos se caracterizan por implementar combinaciones de los algoritmos PWM continuos y discontinuos, buscando mejorar características del proceso de conversión de energía. Entre las propuestas realizadas se destacan el GDPWM y el HDPWM.

# 4.10.1 MÉTODO PWM DISCONTINUO GENERALIZADO (GENERALIZED DISCONTINUOUS PWM [GDPWM])

Hava (1998) propone el modulador GDPWM, el cual permite modificar mediante una variable de control  $\psi$ , la localización de la saturación de las señales moduladoras. Al presentar los métodos DPWM1, DPWM2 y DPWM0, se ilustró que la señal moduladora  $V_i^{**}(t)$  estaba saturada en medio ciclo de fundamental durante intervalos de 60°. Estos intervalos de saturación están localizados a un determinado ángulo  $\psi$  respecto a la posición en que la fundamental  $V_i^*(t)$  presenta su valor máximo.

El algoritmo propuesto por Hava (1998) permite regular este ángulo en el rango [0, 60°] para obtener un conjunto de moduladores discontinuos (entre ellos: DPWM0, DPWM1 y DPWM2) que minimizan las pérdidas por conmutación, en aplicaciones de cargas con ángulos de factor de potencia que varían entre  $[-30^\circ, 30^\circ]$ . Para generar la señal de secuencia cero, las señales fundamentales son desfasadas un ángulo de ψ-30° y de las tres nuevas señales:  $V_{ax}^*, V_{bx}^*, V_{cx}^*$  la de mayor magnitud absoluta es saturada.

## 4.10.2 MÉTODO PWM HÍBRIDO DISCONTINUO (HYBRID DISCONTINUOUS PWM [HDPWM])

López, Camacho, Díaz, Gaviria y Bolaños (2009) proponen el modulador HDPWM, una solución capaz de escoger el algoritmo de modulación de mejor desempeño armónico de acuerdo con las condiciones de operación, específicamente: índice de modulación M y ángulo de fase θ. Esta solución híbrida presenta un desempeño armónico superior al exhibido por la técnica convencional SVPWM y su esquema de desarrollo es apropiado para implementaciones digitales (Camacho y López, 2007).

## 4.10.3 MODULACIÓN PWM DE VECTORES ESPACIALES (SVPWM)

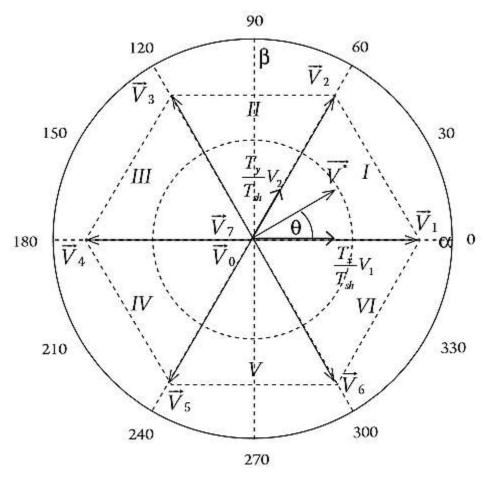

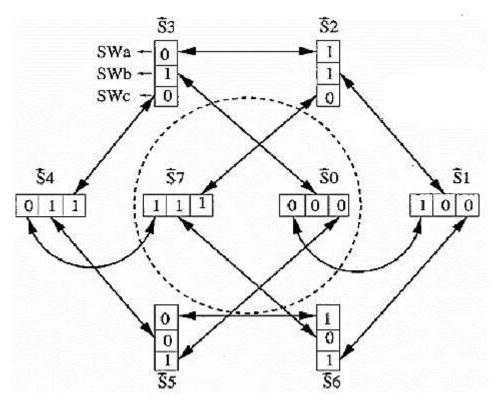

Este enfoque implica la síntesis de un vector espacial de referencia  $V^*$  en el plano  $\alpha\beta$  mediante aplicación instantánea de los estados posibles de un VSI. Los ocho vectores espaciales de voltaje posibles en un VSI trifásico de dos niveles se pueden clasificar en dos grupos: vectores activos ( $V_1-V_6$ ) y vectores cero ( $V_0$  y  $V_7$ ); estos se ilustran en la figura 4.25. Los vectores activos poseen igual magnitud y están desfasados mutuamente 60°, por tanto, pueden ser expresados mediante la ecuación 4.11. (Camacho, López, Díaz, & Gaviria, 2012).

$$V_K = \frac{2}{3} V_{dc} e^{\frac{j(k-1)}{3}}$$

Para  $k = 1, 2, ... 6.$  (4.11)

En donde k es uno de los sectores del hexágono. Como se ilustra en la figura 4.25, los vectores dividen el plano complejo en seis sectores (I-VI), formando un hexágono en el plano  $\alpha\beta$ . Cualquier vector de referencia  $V^*$  dentro de los límites del hexágono puede ser sintetizado mediante descomposición en sus vectores de voltaje adyacentes. (Camacho, López, Díaz, & Gaviria, 2012).

Por lo tanto, el vector espacial de voltajes de fase del estator puede ser representado en términos de los voltajes en el inversor como se muestra en la ecuación 4.12.

$$\overrightarrow{v_s}(t) = \frac{2}{3} \left( v_{aN} e^{j0} + v_{bN} e^{\frac{j2\pi}{3}} + v_{cN} e^{\frac{j4\pi}{3}} \right)$$

(4.12)

Existen dos restricciones de operación para el inversor trifásico:

- Nunca se puede cortocircuitar la fuente DC, lo que se traduce en que en una misma rama no pueden conducir los dos conmutadores a la vez.

- Nunca se debe dejar en circuito abierto las inductancias del lado de la carga, lo que se traduce en que siempre debe haber algún semiconductor conduciendo en cada rama.

Teniendo en cuenta estas restricciones, es posible definir una función de conmutación en cada rama del inversor como se muestra a continuación.

- 1 para cuando el conmutador superior está encendido y el inferior apagado.

- *0* para cuando el conmutador superior está apagado y el inferior encendido.

Al tener presentas las restricciones y la función de conmutación se obtiene el vector espacial  $\overrightarrow{v_s}(t)$  como sigue:

$$\overrightarrow{v_S}(t) = \frac{2}{3} V_{dc} \left( SW_a e^{j0} + SW_b e^{\frac{j2\pi}{3}} + SW_c e^{\frac{j4\pi}{3}} \right)$$

(4.13)

Esta ecuación solo puede tomar 8 valores diferentes y cada uno de estos valores está asociado a un estado del inversor; cada cambio de estado del inversor se puede considerar como una conmutación del inversor. Estos estados se ilustran en la figura 4.24, al reemplazar el valor de los estados del inversor se obtienen los valores instantáneos del vector espacial  $\overrightarrow{v_s}(t)$  que puede generar el inversor. Estos se resumen en la tabla 4.2, donde a cada estado j, se ha asociado a un vector  $\overrightarrow{V_j}$ . (Camacho, López, Díaz, & Gaviria, 2012).

**Figura 4.24.** Estados posibles de los interruptores. (Camacho, López, Díaz, & Gaviria, 2012).

| Estados | Función de conmutación |        |                 | Vectores                     | Valeres                                |

|---------|------------------------|--------|-----------------|------------------------------|----------------------------------------|

| $S_J$   | $SW_a$                 | $SW_B$ | SW <sub>c</sub> | $\overrightarrow{V_{J}}$     | Valores                                |

| $S_0$   | 0                      | 0      | 0               | $\overrightarrow{V_0}$ (000) | 0                                      |

| $S_1$   | 1                      | 0      | 0               | $\overrightarrow{V_1}$ (100) | $\frac{2}{3}V_{dc}e^{j0}$              |

| $S_2$   | 1                      | 1      | 0               | $\overrightarrow{V_2}$ (110) | $\frac{2}{3}V_{dc}e^{\frac{j\pi}{3}}$  |

| $S_3$   | 0                      | 1      | 0               | $\overrightarrow{V_3}$ (010) | $\frac{2}{3}V_{dc}e^{\frac{j2\pi}{3}}$ |

| $S_4$   | 0                      | 1      | 1               | $\overrightarrow{V_4}$ (011) | $\frac{2}{3}V_{dc}e^{J\pi}$            |

| $S_5$   | 0                      | 0      | 1               | $\overrightarrow{V}_5$ (001) | $\frac{2}{3}V_{dc}e^{\frac{j4\pi}{3}}$ |

| $S_6$   | 1                      | 0      | 1               | $\overrightarrow{V_6}$ (101) | $\frac{2}{3}V_{dc}e^{\frac{j5\pi}{3}}$ |

| $S_7$   | 1                      | 1      | 1               | $\overrightarrow{V_7}$ (111) | 0                                      |

**Tabla 4.2.** Vectores de voltajes instantáneos del inversor. (Camacho, López, Díaz, & Gaviria, 2012).

En aras de mejorar el desempeño armónico, la síntesis del vector referencia se complementa con la aplicación de los vectores cero (Narayanan, 1999). Considere la descomposición ilustrada en la figura 4.25, donde el vector referencia  $V^*$  se ubica en el sector I, por tanto:

$$\vec{V}^* = \frac{T_x}{T_{sh}} V_1 + \frac{T_y}{T_{sh}} V_2 \tag{4.14}$$

Donde:

$T_{sh}$  corresponde a medio ciclo de conmutación.

$T_x$ ,  $T_y$  son los tiempos de activación de los vectores activos (en este caso  $V_1$  y  $V_2$ ).

Al considerar un conjunto trifásico balanceado, el vector de voltaje de referencia describe una trayectoria circular como la ilustrada con línea punteada en la figura 4.25. De esta manera, cualquier voltaje de referencia deseado puede ser descrito por la ecuación 4.15.

$$\vec{V}^*(t) = M \frac{V_{dc}}{2} e^{j2\pi f_m t} = M \frac{V_{dc}}{2} e^{j\omega_n}$$

(4.15)

Figura 4.25. Hexágono del inversor. (Camacho, López, Díaz, & Gaviria, 2012).

### 4.11 SECUENCIAS DE CONMUTACIÓN

La secuencia de conmutación hace referencia, al orden de aplicación establecido para los vectores del inversor que aproximarán al vector de referencia dentro de un ciclo de conmutación. Esta secuencia no es única, ya que existen diferentes combinaciones que arrojan el mismo valor medio del voltaje deseado en términos de los vectores adyacentes que delimitan el sector. Sin embargo, el criterio que generalmente se adopta es el de mínimas pérdidas por conmutación, seleccionando aquellas transiciones de estado que provocan la conmutación en una sola rama del inversor.

Por ejemplo, se permite la transición del estado al estado puesto que solo necesita la conmutación de la rama en el inversor, en tanto que la transición del estado al no es permitida ya que precisa la transición en más una rama del inversor. La Figura 4.26, ilustra mediante flechas continuas las transiciones permitidas, en ella es importante notar como a partir de los estados cero es posible pasar a cualquier estado activo y viceversa. (Camacho, López, Díaz, & Gaviria, 2012).

Además de tener en cuenta las transiciones permitidas, se recomienda empezar y acabar la secuencia de conmutación con un vector cero (Narayanan, 1999), esto con el fin

de conservar las simetrías de cuarto de onda, media onda y tres fases en la señal modulada; una secuencia apropiada es. (Camacho, López, Díaz, & Gaviria, 2012).

Figura 4.26. Transiciones de estado permitidas. (Zhou, 2002).

Resolviendo  $T_x$  y  $T_y$  de la ecuación 4.14 mediante substitución de  $V_1$  y  $V_2$  de la ecuación 4.11 para el voltaje de referencia definido en la ecuación 4.15 se obtienen la expresión de la ecuación 4.16, válida para el cálculo de  $T_x$  y  $T_y$  dentro del sector I. Al generalizar para los seis sectores se obtiene la ecuación 4.17, en donde k es el sector en el que se ubica el vector de referencia (k+1=1 para k=6). (Camacho, López, Díaz, & Gaviria, 2012).

$$T_{x} = T_{sh} M \frac{\sqrt{3}}{2} \sin\left(\frac{\pi}{3} - \theta\right)$$

$$T_{y} = T_{sh} M \frac{\sqrt{3}}{2} \sin(\theta)$$

$$T_{k} = T_{sh} M \frac{\sqrt{3}}{2} \sin\left(\frac{k\pi}{3} - \theta\right)$$

(4.16)

$$T_{k+1} = T_{sh} M \frac{\sqrt{3}}{2} \sin\left(\theta - (k-1)\frac{\pi}{3}\right)$$

(4.17)

La diferencia entre  $T_{sh}$  y  $T_x$ ,  $T_y$  corresponde al tiempo de activación de los vectores cero  $(T_z)$ , generalmente, este tiempo se divide en partes iguales entre  $T_0$  y  $T_7$ . Sin embargo, existen otras alternativas de distribución de tiempo cero, estas pueden ser representadas

mediante la ecuación 4.18, en donde  $K_0(\omega_m t)$  es el distribuidor de estados cero  $[1 \ge K_0(\omega_m t) \ge 0]$  (Zhou, 2002).

$$T_7 = K_0(\omega_m t) T_z$$

$$T_0 = (1 - K_0(\omega_m t)) T_z$$

(4.18)

Las alternativas más comunes en la selección de  $K_0$  se resumen en la tabla 4.3; cada una de ellas se asocia con uno de los algoritmos de modulación PWM continuos o discontinuos ya descritos.

|                               | <i>k</i> PAR                                   | k IMPAR                                        |

|-------------------------------|------------------------------------------------|------------------------------------------------|

| $K_0$ sy-svpwm $(\omega_m t)$ | 1/2                                            | 1/2                                            |

| $K_0$ sрwм $(\omega_m t)$     | $1/2 + (T_1-T_2)/6T_Z$                         | $1/2 + (T_1-T_2)/6T_Z$                         |

| $K_0$ DPWM0 $(\omega_m t)$    | 1                                              | 0                                              |

| $K_{0}$ DPWM1 $(\omega_{m}t)$ | 0, primera mitad del sector; 1, segunda mitad. | 1, primera mitad del sector; 0, segunda mitad. |

| $K_0$ ррwм2 $(\omega_m t)$    | 0                                              | 1                                              |

| $K_0$ ррwмз $(\omega_m t)$    | 1, primera mitad del sector; 0, segunda mitad. | 0, primera mitad del sector; 1, segunda mitad. |

| $K_0$ DPWMMax $(\omega_m t)$  | 1                                              | 1                                              |

| $K_0$ dpwmmin $(\omega_m t)$  | 0                                              | 0                                              |

**Tabla 4.3.** Alternativas de selección de  $K_0$ . (Camacho, López, Díaz, & Gaviria, 2012).

# 4.12 CARACTERÍSTICAS DE LAS TÉCNICAS DE MODULACIÓN PWM

- **1. Enfoque:** Determina la forma de implementación del modulador PWM, existen dos opciones: la modulación basada en portadora (CB-PWM) y la modulación basada en vectores espaciales (SV-PWM). La CB-PWM resulta apropiada para la presentación de conceptos de modulación en ambientes académicos, sin embargo, es poco utilizada en la práctica. La SV-PWM resulta ser más compleja, sin embargo, es la más utilizada en implementaciones digitales. (Camacho, López, Díaz, & Gaviria, 2012).

- **2. Algoritmo de modulación:** Establece la estrategia de conmutación de las ramas del inversor VSI. Se divide en tres grupos como se explicó anteriormente: a) algoritmos continuos b) algoritmos discontinuos y c) algoritmos híbridos. (Camacho, López, Díaz, & Gaviria, 2012).

- **3. Control de flanco:** Indica el flanco del pulso PWM que varía durante la modulación. Existen tres alternativas: flanco doble, flanco de subida y flanco de bajada. Esta característica está asociada a la forma de la señal triangular como ya se expuso. La selección de control de flanco incide directamente sobre las pérdidas de energía en los conmutadores del inversor, siendo que, a mayor cantidad de conmutaciones, mayores pérdidas. (Camacho, López, Díaz, & Gaviria, 2012).

- **4. Sincronismo:** Está definido por la relación entre frecuencias portadora y moduladora como fue definido. El modulador asincrónico produce subarmónicos a frecuencias que no son múltiplos enteros de la frecuencia moduladora; sin embargo, para valores grandes de N (N > 21) la amplitud de estos sub-armónicos es muy pequeña. De otro lado, el modulador sincrónico es apropiado para aplicaciones que exigen un bajo índice de frecuencia (N < 21), es decir, aplicaciones de alta potencia. (Camacho, López, Díaz, & Gaviria, 2012).

- **5. Simetría:** Depende de la técnica de muestreo de la señal moduladora. Cuando el muestreo es hecho en solamente uno de los picos de la portadora (positivo o negativo) se tiene el muestreo simétrico, de lo contrario, el muestreo es asimétrico. Ambas alternativas de simetría generan un bajo contenido armónico en el voltaje de salida del inversor, siendo comparativamente superior el producido por el PWM asimétrico (Holmes, 1998) y (Camacho, López, Díaz, & Gaviria, 2012).

La tabla 4.4 presenta una clasificación de las técnicas de modulación PWM modernas con base en las características identificadas. Este conjunto de características permite clasificar las propuestas de modulación en el área del control de inversores VSI para aplicaciones de control de motores de inducción. Con este grupo de características se espera facilitar el proceso de comparación entre las diversas técnicas de modulación PWM y, asimismo, aportar para el desarrollo de nuevos algoritmos que permitan la evolución de propuestas en esta área. (Camacho, López, Díaz, & Gaviria, 2012).

| CARACTERÍSTICAS   | ALTERNATIVAS                                    |  |

|-------------------|-------------------------------------------------|--|

| Enfoque           | Basado en portadora (CB-PWM).                   |  |

| Lilloque          | Basado en vectores espaciales (SV-PWM).         |  |

|                   | Continuo: SPWM, THIPWM1/6, THIPWM1/4, SY-SVPWM. |  |

| Algoritmo de      | Discontinuo: DPWM0, DPWM1, DPWM2, DPWM3,        |  |

| modulación        | DPWMMax, DPWMMin.                               |  |

|                   | Híbrido: GDPWM, HDPWM.                          |  |

|                   | Flanco de subida.                               |  |

| Control de flanco | Flanco de bajada.                               |  |

|                   | Doble flanco.                                   |  |

| Sincronismo       | Sincrónico.                                     |  |

| Sincromsino       | Asincrónico.                                    |  |

| Simetría          | Simétrico.                                      |  |

| Simetria          | Asimétrico.                                     |  |

**Tabla 4.4.** Resumen de las características concluidas. (Camacho, López, Díaz, & Gaviria, 2012).

Las características concluidas abordan los aspectos fundamentales para realizar comparaciones objetivas entre técnicas de modulación, permiten el uso de un lenguaje común durante dichas comparaciones y son definidas de forma genérica con el propósito de incluir la caracterización de futuros esquemas de modulación PWM. el objetivo de los autores es que la estructura aquí presentada, estimule la discusión en la comunidad científica y permita una interpretación de mayor didáctica en los ambientes académicos. (Camacho, López, Díaz, & Gaviria, 2012).

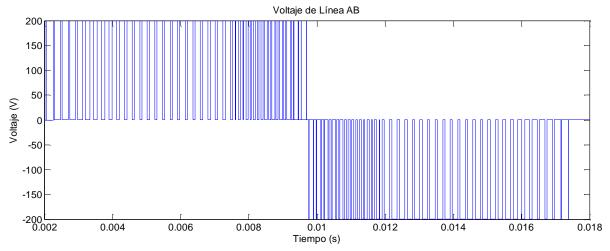

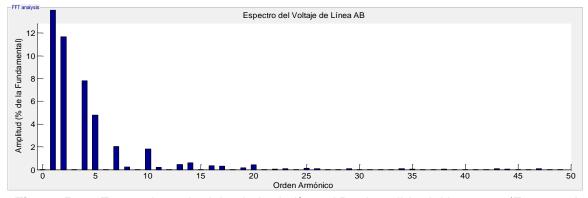

## 5. CAPÍTULO 2: SIMULACIÓN

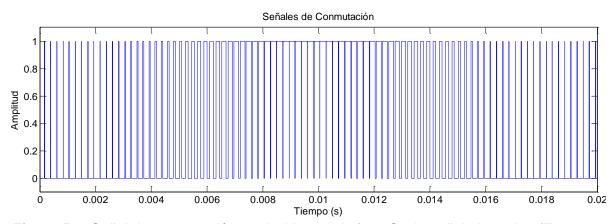

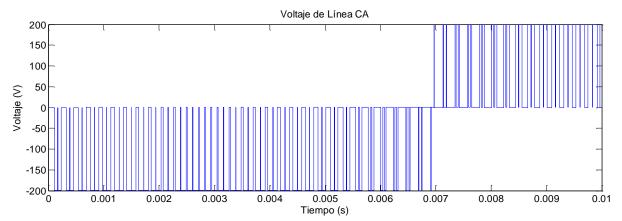

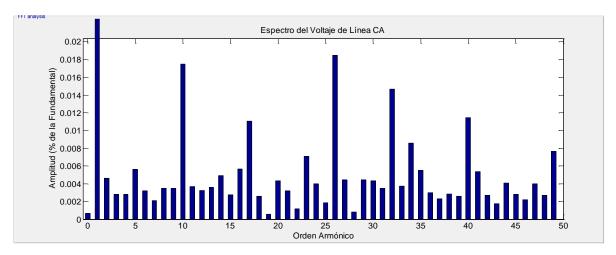

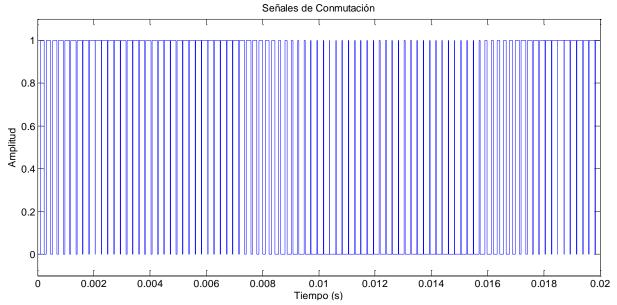

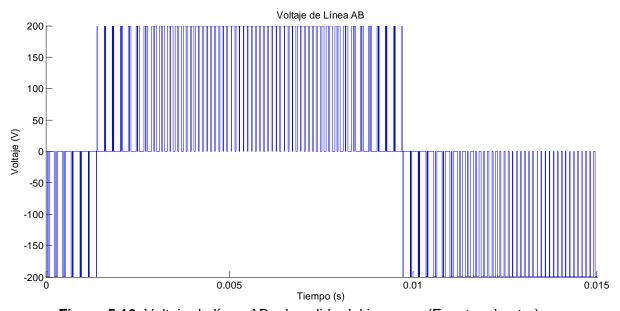

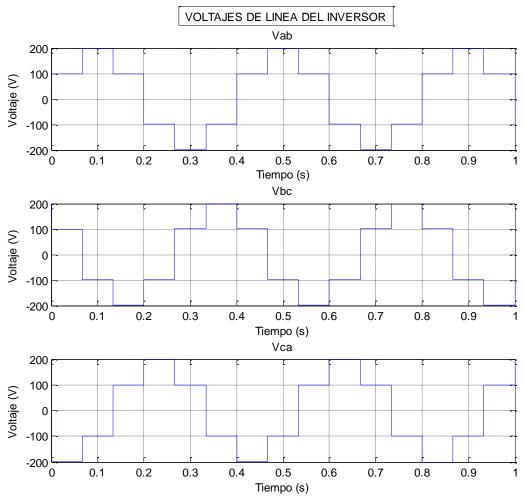

Para poder generar una onda de voltaje deseada a la salida de un inversor, es necesario poder comandar adecuadamente el encendido y el apagado de los dispositivos de potencia. Las estrategias de comando vistas anteriormente se encargan de generar los patrones de conmutación adecuados para generar dicho voltaje de salida, el voltaje realmente interesante en estos inversores son los voltajes de línea.

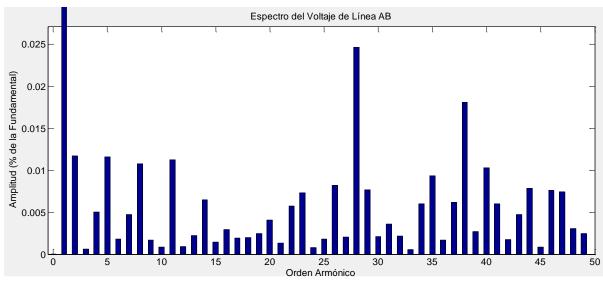

En este apartado se detallan las estrategias de modulación que se aplicaron al inversor trifásico con el fin de determinar cuál es más factible respecto a la aplicación que tendrá el inversor, además de considerar su eficiencia y calidad de energía.

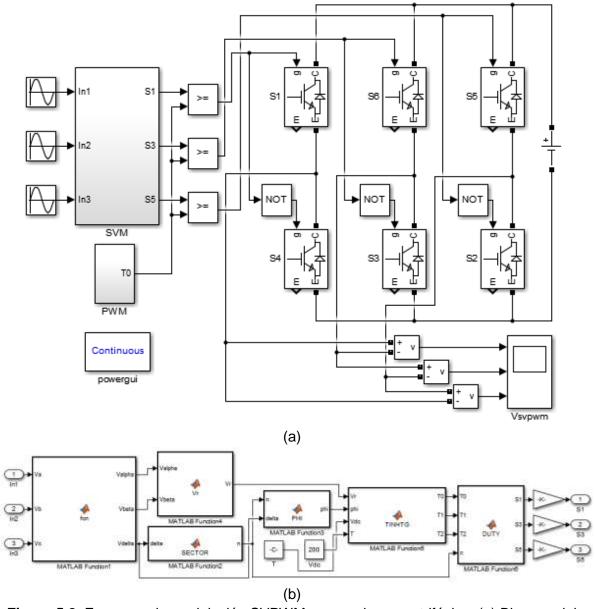

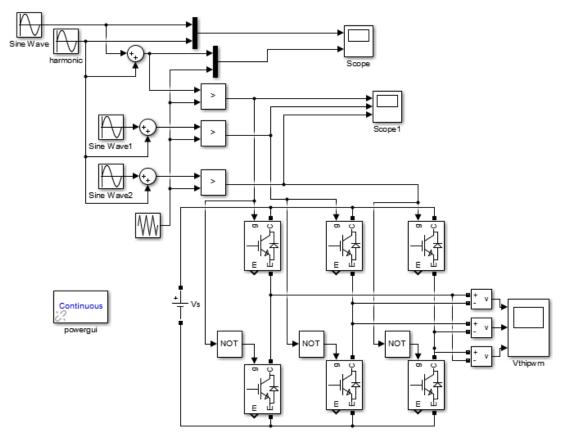

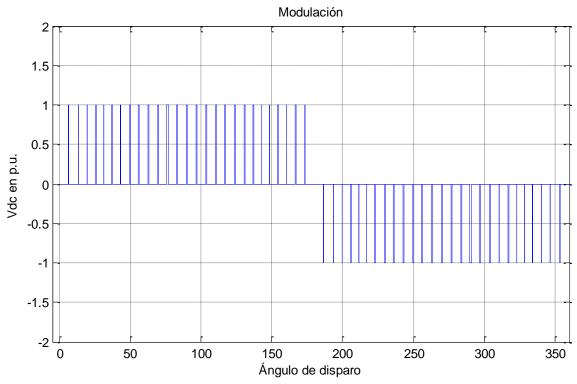

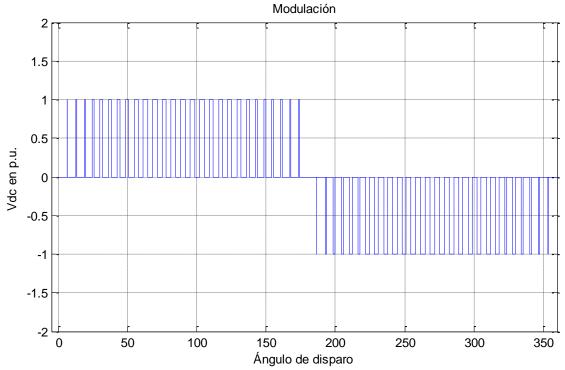

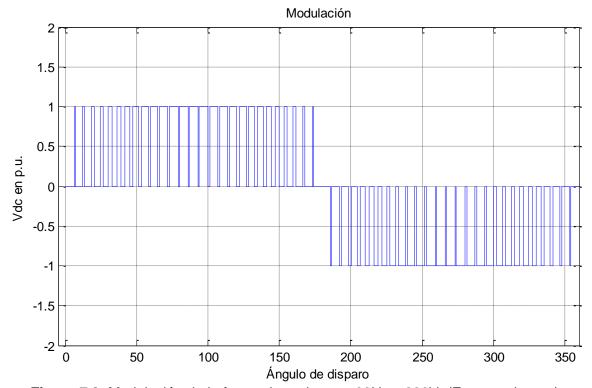

De los diferentes tipos de modulación PWM propuestos anteriormente se han seleccionado el *SPWM*, el *SVPWM* y el *THIPWM* para el desarrollo de la simulación debido a la aplicación que se le piensa dar al inversor, el cual se conectará a un motor asíncrono. Estas simulaciones se realizaron en el Simulink® del Matlab®, esta herramienta es de gran utilidad dentro del campo de la electrónica de potencia debido a que el entorno de Simulink® tiene una gran capacidad para simulaciones de comando, lo cual mejora las respuestas de simulación de los circuitos. Del programa se extrajo el esquema y las formas de onda de voltaje de líneas. Además, se realizó un análisis FFT (Fast Fourier Transform – "Transformada Rápida de Fourier") para cada simulación. Se presentará a continuación cada modulación seleccionada.

### **5.1 SPWM**

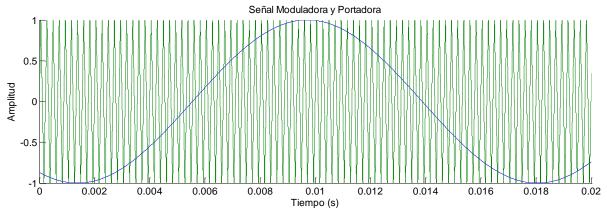

La estrategia de modulación por ancho de pulso sinusoidal, debido a su fácil implementación, es la técnica más usada en la familia de inversores, además, esta técnica se puede emplear con algunas modificaciones. La idea básica es la de comparar una onda sinusoidal con una señal portadora para obtener los pulsos necesarios para cada interruptor.

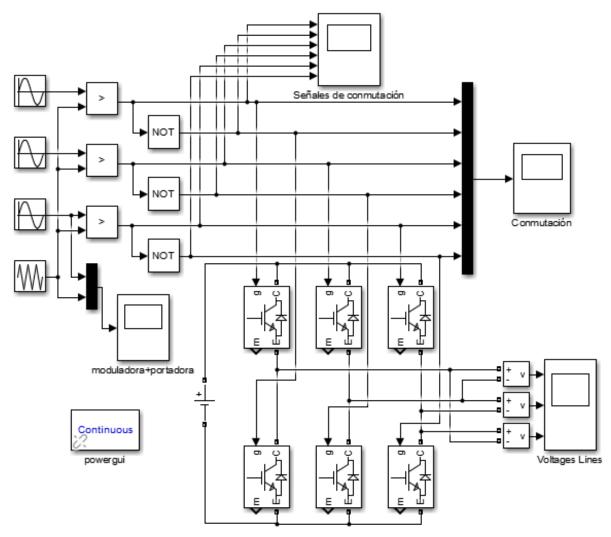

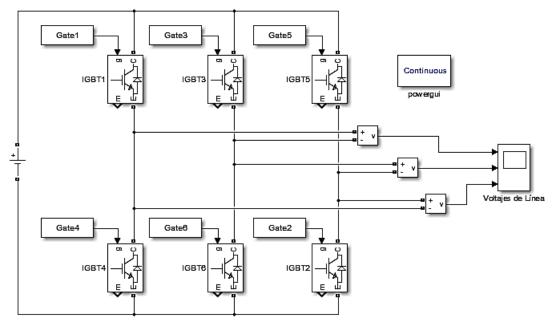

Para este tipo de modulación se utilizó el siguiente esquema que contempla tres ondas sinusoidales desfasadas entre ellas 120°, un bloque comparador, un bloque negador "NOT", IGBT's con Diodos configurados como tipo puente y una fuente de voltaje en CD para alimentar a los semiconductores.

Las señales de comando obtenidas a partir de la comparación de una onda moduladora con las ondas portadoras deben cumplir algunas características para poder mantener al máximo la simetría de la onda. (Holmes Grahame & Lipo, 2003).

- La onda sinusoidal y la triangular deben estar sincronizadas, es decir, deben iniciarse en el mismo instante.

- La frecuencia de la portadora debe ser alta. Comúnmente el índice de frecuencia "mf" debe ser mayor a 21, esto con el fin de obtener una THD reducida a la salida.

En la figura 5.1 se muestra el esquema utilizado para la modulación SPWM con cada uno de sus bloques y la conexión para medir los voltajes de línea del inversor.

**Figura 5.1.** Esquema de la modulación SPWM para un inversor trifásico. (Fuente: el autor).

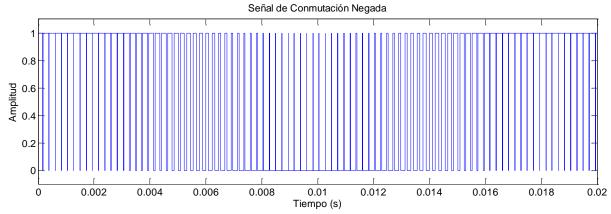

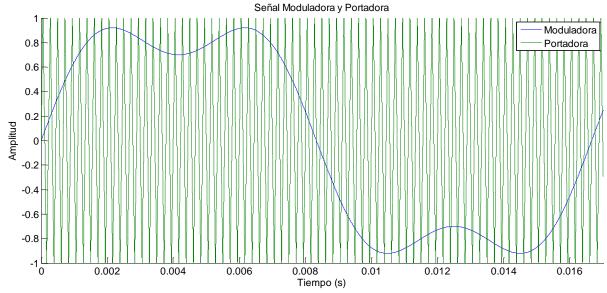

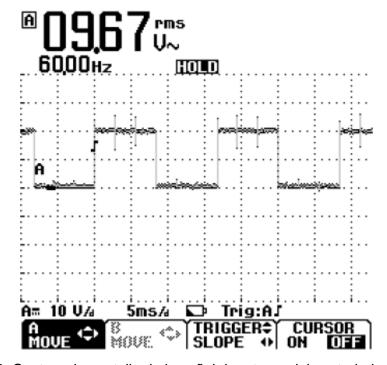

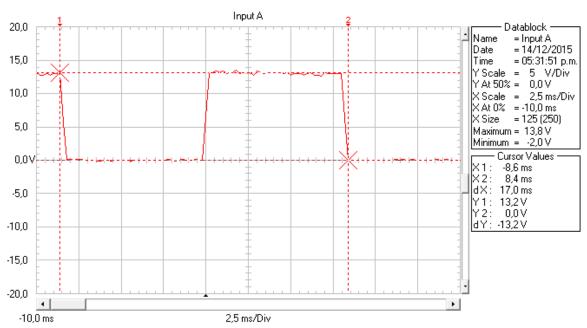

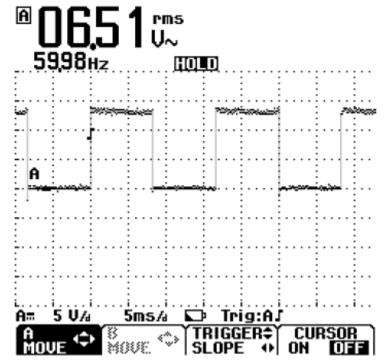

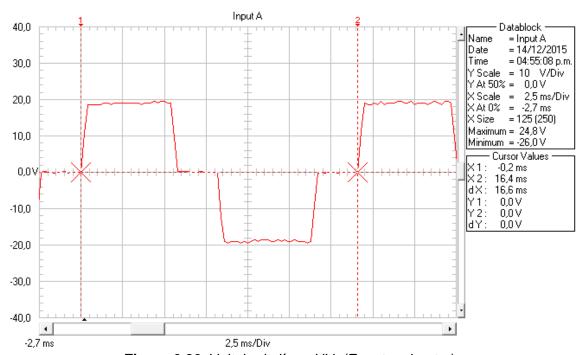

A continuación, en la figura 5.2 se puede visualizar la señal moduladora y la portadora en este caso, la señal moduladora es la de la fase C como se mostró en la figura anterior.

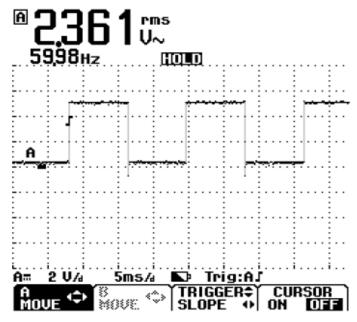

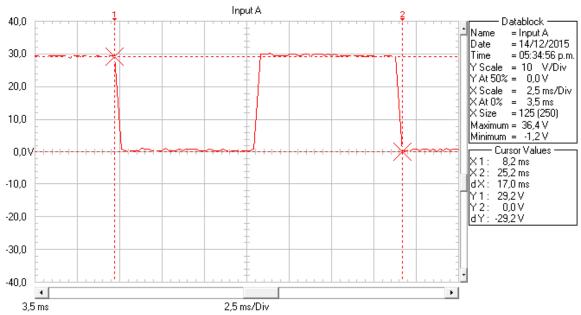

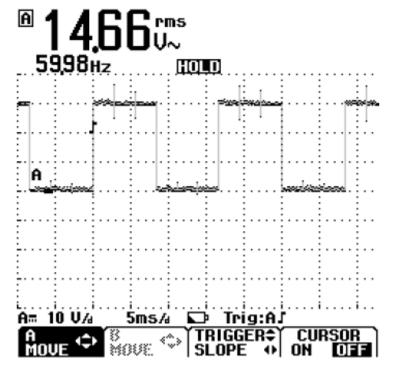

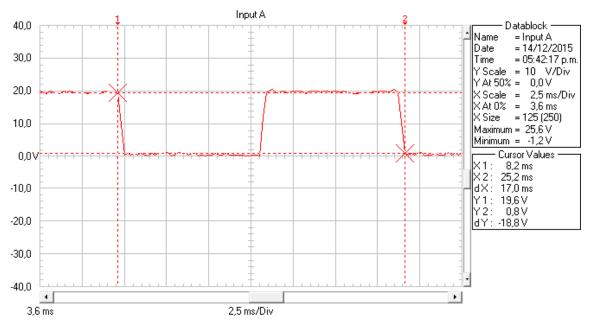

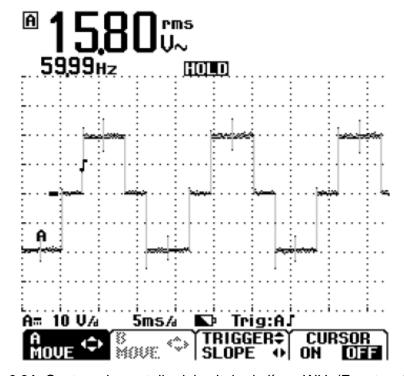

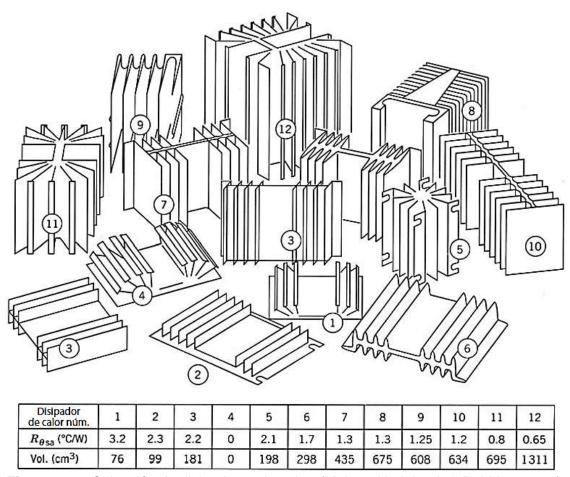

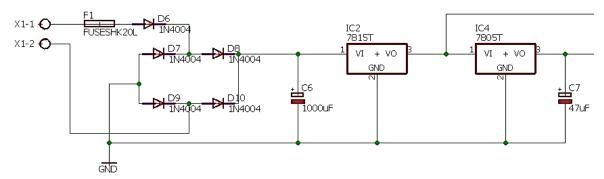

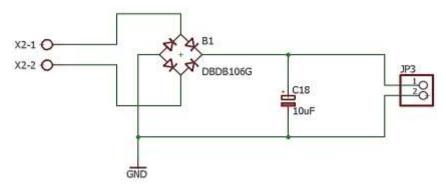

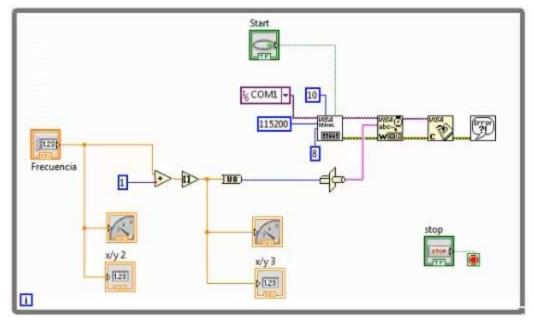

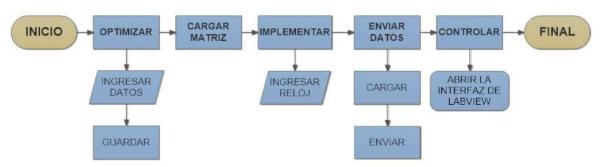

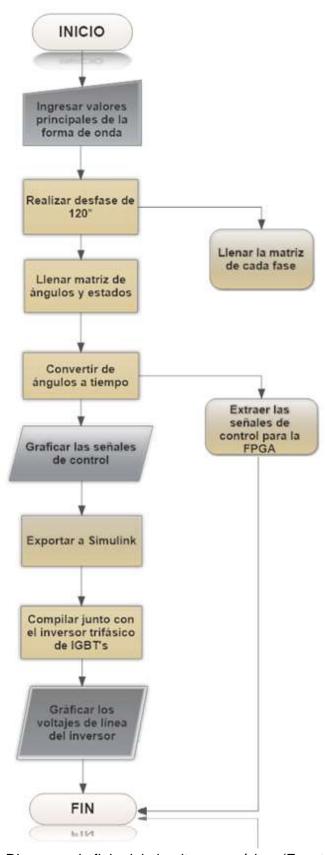

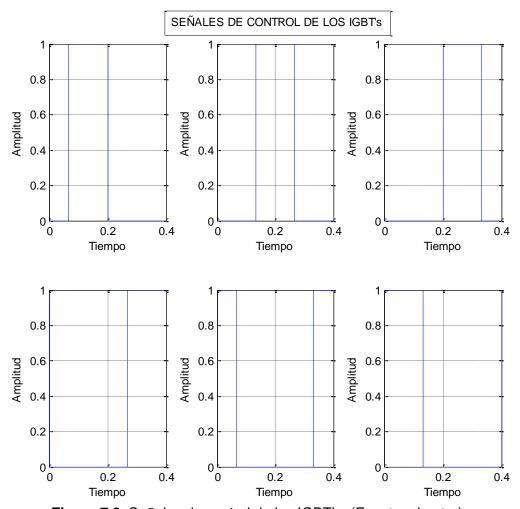

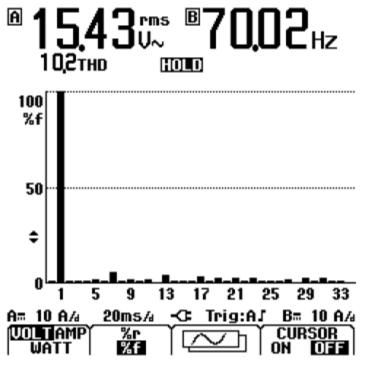

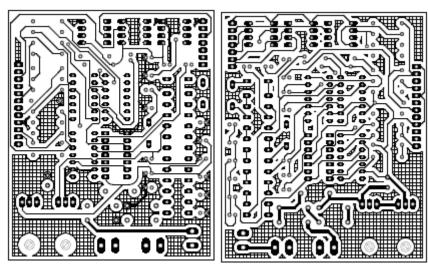

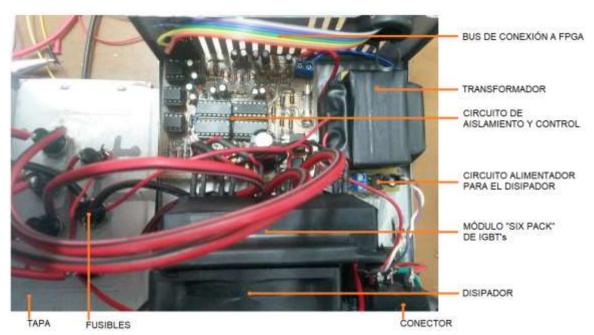

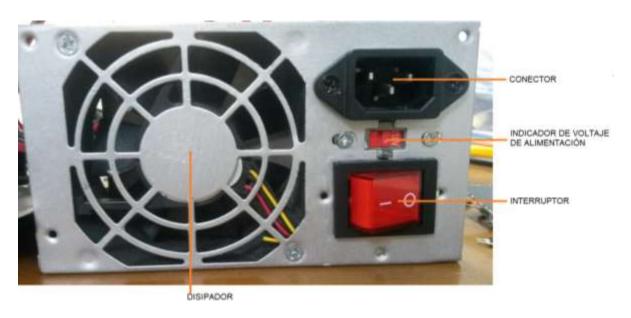

**Figura 5.2.** Señal moduladora (sinusoidal) y señal portadora (triangular). (Fuente: el autor).